## **Functional restrictions**

- Pre loading data size is limited to MAX\_PRE\_LOADING\_DATA\_SIZE[21-18] regardless of using Production State Awareness function.

- MAX\_PRE\_LOADING\_DATA\_SIZE[21-18] value will change when host sets Enhanced User area Partition.

# **Reliability Guidance**

This reliability guidance is intended to notify some guidance related to using raw NAND flash. Although random bit errors may occur during use, it does not necessarily mean that a block is bad. Generally, a block should be marked as bad when a program status failure or erase status failure is detected. The other failure modes may be recovered by a block erase. ECC treatment for read data is mandatory due to the following Data Retention and Read Disturb failures.

### -Write/Erase Endurance

Write/Erase endurance failures may occur in a cell, page, or block, and are detected by doing a status read after either an auto program or auto block erase operation. The cumulative bad block count will increase along with the number of write/erase cycles.

### -Data Retention

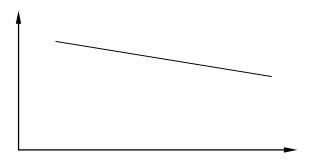

The data in memory may change after a certain amount of storage time. This is due to charge loss or charge gain. After block erasure and reprogramming, the block may become usable again. Also write/erase endurance deteriorates data retention capability. The figure below shows a generic trend of relationship between write/erase endurance and data retention.

### -Read Disturb

A read operation may disturb the data in memory. The data may change due to charge gain. Usually, bit errors occur on other pages in the block, not the page being read. After a large number of read cycles (between block erases), a tiny charge may build up and can cause a cell to be soft programmed to another state. After block erasure and reprogramming, the block may become usable again.

Considering the above failure modes, TOSHIBA recommends following usage:

- Please avoid any excessive iteration of resets and initialization sequences (Device identification mode) as far as possible after power-on, which may result in read disturb failure. The resets include hardware resets and software resets.

- e.g.1) Iteration of the following command sequence, CMD0 CMD1 --The assertion of CMD1 implies a count of internal read operation in Raw NAND.

CMD0: Reset command, CMD1: Send operation command

- e.g.2) Iteration of the following commands, CMD30 and/or CMD31 CMD30: Send status of write protection bits, CMD31: Send type of write protection