Publication # **48063** Revision: **3.24** Issue Date: **September 2014**

Advanced Micro Devices 🗖

#### © 2010-2014 Advanced Micro Devices, Inc. All rights reserved.

The information contained herein is for informational purposes only, and is subject to change without notice. While every precaution has been taken in the preparation of this document, it may contain technical inaccuracies, omissions and typographical errors, and AMD is under no obligation to update or otherwise correct this information. Advanced Micro Devices, Inc. makes no representations or warranties with respect to the accuracy or completeness of the contents of this document, and assumes no liability of any kind, including the implied warranties of noninfringement, merchantability or fitness for particular purposes, with respect to the operation or use of AMD hardware, software or other products described herein. No license, including implied or arising by estoppel, to any intellectual property rights is granted by this document. Terms and limitations applicable to the purchase or use of AMD's products are as set forth in a signed agreement between the parties or in AMD's Standard Terms and Conditions of Sale.

#### Trademarks

AMD, the AMD Arrow logo, AMD FX, AMD Opteron, and combinations thereof, are trademarks of Advanced Micro Devices, Inc.

HyperTransport is a licensed trademark of the HyperTransport Technology Consortium.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

#### AMDA h-0Fh Processors

# **List of Figures**

# **List of Tables**

| Table 1. Arithmetic and Logic Operators                                           | 8  |

|-----------------------------------------------------------------------------------|----|

| Table 2. CPUID Values for AMD Family 15h Models 00h-0Fh G34r1 Processor Revisions |    |

| Table 3. CPUID Values for AMD Family 15h Models 00h-0Fh C32r1 Processor Revisions | 9  |

| Table 4. CPUID Values for AMD Family 15h Models 00h-0Fh AM3r2 Processor Revisions | 10 |

| Table 5. Supported Mixed Revision Configurations                                  | 11 |

| Table 6. Cross Reference of Product Revision to OSVW ID.                          |    |

| Table 7. Cross-Reference of Processor Revision to Errata                          | 14 |

| Table 8. Cross-Reference of Errata to Package Type                                | 18 |

| Table 9. Cross-Reference of Errata to Processor Segments                          |    |

# **Revision History**

| Date           | Revision                                                                                                                                                                                                                                                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| September 2014 | 3.24                                                                                                                                                                                                                                                                                                       | Added erratum #775, #778, #786, and #815.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| October 2012   | 3.18                                                                                                                                                                                                                                                                                                       | Added AMD Opteron <sup>™</sup> 3300 Series, 4300 Series, 6300 Series Processors and OR-C0 silicon revision to Overview and Tables 2-8. Added Mixed Processor Revision Support. Added errata #685, #699, #704, #707, #708, #727, #734, #739, and #759. Updated erratum #668.                                                                                                                                                                                                                   |  |

| August 2012    | 3.16                                                                                                                                                                                                                                                                                                       | Added errata #737, #740, #742, #744. and #745; Updated erratum #709.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| May 2012       | 3.12                                                                                                                                                                                                                                                                                                       | Added AMD Opteron <sup>™</sup> 3200 Series Processor to Overview, Table 4, and Table 9; Updated MSRC001_0141<br>OS Visible Work-around MSR1 (OSVW_Status) section for errata #724; Added errata #691,#709, #714, #717-<br>#720, #724-#726; Removed erratum #534 as this is redundant with, and replaced by, errata #717 and #718;<br>Changed Fix Planned to "Yes" for errata #520, #535-#538, #586, #592, #593, #600, #619, #623, #624, #636,<br>#658, #659, #660, #668, #671-#675, and #689. |  |

| November 2011  | mber 2011       3.04       Added errata #600, #693-#695, and #709. Updated errata #534 and #671. Added package types G34, C32         Table 8. Added AMD Opteron <sup>™</sup> 4200 Series Processor and AMD Opteron <sup>™</sup> 6200 Series Processor to Overview and Table 9. Added Table 2 and Table 3. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| October 2011   | 3.00                                                                                                                                                                                                                                                                                                       | Initial public release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

Revision Guide for AMD Family 15h Models 00h-0Fh Processors

# **Overview**

The purpose of the *Revision Guide for AMD Family 15h Models 00h-0Fh Processors* is to communicate updated product information to designers of computer systems and software developers. This revision guide includes information on the following products:

- AMD FX<sup>™</sup>-Series Processor

- AMD Opteron<sup>™</sup> 3200 Series Processor

- AMD Opteron<sup>™</sup> 3300 Series Processor

- AMD Opteron<sup>™</sup> 4200 Series Processor

- AMD Opteron<sup>™</sup> 4300 Series Processor

- AMD Opteron<sup>™</sup> 6200 Series Processor

- AMD Opteron<sup>™</sup> 6300 Series Processor

Feature support varies by brands and OPNs. To determine the features supported by your processor, contact your customer representative.

This guide consists of these major sections:

- Processor Identification shows how to determine the processor revision and workaround requirements, and to construct, program, and display the processor name string.

- Product Errata provides a detailed description of product errata, including potential effects on system operation and suggested workarounds. An erratum is defined as a deviation from the product's specification, and as such may cause the behavior of the processor to deviate from the published specifications.

- Documentation Support provides a listing of available technical support resources.

### **Revision Guide Policy**

Occasionally, AMD identifies product errata that cause the processor to deviate from published specifications. Descriptions of identified product errata are designed to assist system and software designers in using the processors described in this revision guide. This revision guide may be updated periodically.

# **Conventions**

### Numbering

- **Binary numbers**. Binary numbers are indicated by appending a "b" at the end, e.g., 0110b.

- **Decimal numbers**. Unless specified otherwise, all numbers are decimal. This rule does not apply to the register mnemonics.

- Hexadecimal numbers. Hexadecimal numbers are indicated by appending an "h" to the end, e.g., 45F8h.

- Underscores in numbers. Underscores are used to break up numbers to make them more readable. They do not imply any operation. e.g., 0110\_1100b.

- Undefined digit. An undefined digit, in any radix, is notated as a lower case "x".

### **Register References and Mnemonics**

In order to define errata workarounds it is sometimes necessary to reference processor registers. References to registers in this document use a mnemonic notation consistent with that defined in the *BIOS and Kernel Developer's Guide (BKDG) for AMD Family 15h Models 00h-0Fh Processors*, order# 42301. Each mnemonic is a concatenation of the register-space indicator and the offset of the register. The mnemonics for the various register spaces are as follows:

- IOXXX: x86-defined input and output address space registers; XXX specifies the byte address of the I/O register in hex (this may be 2 or 3 digits). This space includes the I/O-Space Configuration Address Register (IOCF8) and the I/O-Space Configuration Data Port (IOCFC) to access configuration registers.

- DZFYxXXX: PCI-defined configuration space at bus 0; Z specifies the PCI device address in hex; XXX specifies the byte address of the configuration register (this may be 2 or 3 digits) in hex; Y specifies the function number. For example, D18F3x40 specifies the register at bus 0, device 18h, function 3, address 40h. Some registers in D18F2xXXX have a \_dct[1:0] mnemonic suffix, which indicates there is one instance per DRAM controller (DCT). The DCT instance is selected by DCT Configuration Select[DctCfgSel] (D18F1x10C[0]).

- DZFYxXXX\_xZZZZZ: Port access through the PCI-defined configuration space at bus 0; Z specifies the PCI device address in hex; XXX specifies the byte address of the data port configuration register (this may be 2 or 3 digits) in hex; Y specifies the function number; ZZZZZ specifies the port address (this may be 2 to 7 digits) in hex. For example, D18F2x9C\_x1C specifies the port 1Ch register accessed using the data port register at bus 0, device 18h, function 2, address 9Ch. Refer to the *BKDG* for access properties. Some registers in D18F2xXXX\_xZZZZ have a \_dct[1:0] mnemonic suffix, which indicates there is one instance per DRAM controller (DCT). The DCT instance is selected by DCT Configuration Select[DctCfgSel] (D18F1x10C[0]).

- APICXXX: APIC memory-mapped registers; XXX is the byte address offset from the base address in hex (this may be 2 or 3 digits). The base address for this space is specified by the APIC Base Address Register (APIC\_BAR) at MSR0000\_001B.

- CPUID FnXXXX\_XXXX\_RRR\_xYYY: processor capability information returned by the CPUID instruction where the CPUID function is XXXX\_XXXX (in hex) and the ECX input is YYY (if specified). When a register is specified by RRR, the reference is to the data returned in that register. For example, CPUID Fn8000\_0001\_EAX refers to the data in the EAX register after executing CPUID instruction function 8000\_0001h.

- MSRXXXX\_XXXX: model specific registers; XXXX\_XXXX is the MSR number in hex. This space is accessed through x86-defined RDMSR and WRMSR instructions.

- PMCxXXX[Y]: performance monitor events; XXX is the hexadecimal event counter number programmed into MSRC001\_020[A,8,6,4,2,0][EventSelect] (PERF\_CTL[5:0] bits 7:0). Y, when specified, signifies the unit mask programmed into MSRC001\_020[A,8,6,4,2,0][UnitMask] (PERF\_CTL[5:0] bits 15:8).

• NBPMCxXXX[Y]: northbridge performance monitor events; XXX is the hexadecimal event counter number programmed into MSRC001\_024[6,4,2,0][EventSelect] (NB\_PERF\_CTL[3:0] bits 7:0). Y, when specified, signifies the unit mask programmed into MSRC001\_024[6,4,2,0][UnitMask] (NB\_PERF\_CTL[3:0] bits 15:8).

Many register references use the notation "[]" to identify a range of registers. For example, D18F2x[1,0][4C:40] is a shorthand notation for D18F2x40, D18F2x44, D18F2x48, D18F2x4C, D18F2x140, D18F2x144, D18F2x148, and D18F2x14C.

### **Arithmetic and Logical Operators**

In this document, formulas follow some Verilog conventions as shown in Table 1.

| Operator | Definition                                                                                                                                                                                                                                         |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| {}       | Curly brackets are used to indicate a group of bits that are concatenated together. Each set of bits is separated by a comma. E.g., {Addr[3:2], Xlate[3:0]} represents a 6-bit value; the two MSBs are Addr[3:2] and the four LSBs are Xlate[3:0]. |

| I        | Bitwise OR operator. E.g. $(01b   10b = 11b)$ .                                                                                                                                                                                                    |

| I        | Logical OR operator. E.g. (01b    10b == 1b); logical treats multibit operand as 1 if >=1 and produces a 1-bit result.                                                                                                                             |

| &        | Bitwise AND operator. E.g. $(01b \& 10b == 00b)$ .                                                                                                                                                                                                 |

| &&       | Logical AND operator. E.g. (01b && 10b == 1b); logical treats multibit operand as 1 if >=1 and produces a 1-bit result.                                                                                                                            |

| ^        | Bitwise exclusive-OR operator; sometimes used as "raised to the power of" as well, as indicated by the context in which it is used. E.g. $(01b \land 10b = 11b)$ . E.g. $(2^2 = 4)$ .                                                              |

| ~        | Bitwise NOT operator (also known as one's complement). E.g. ( $\sim 10b = 01b$ ).                                                                                                                                                                  |

| !        | Logical NOT operator. E.g. (!10b == 0b); logical treats multibit operand as 1 if >=1 and produces a 1-bit result.                                                                                                                                  |

| ==       | Logical "is equal to" operator.                                                                                                                                                                                                                    |

| !=       | Logical "is not equal to" operator.                                                                                                                                                                                                                |

| <=       | Less than or equal operator.                                                                                                                                                                                                                       |

| >=       | Greater than or equal operator.                                                                                                                                                                                                                    |

| *        | Arithmetic multiplication operator.                                                                                                                                                                                                                |

| /        | Arithmetic division operator.                                                                                                                                                                                                                      |

| <<       | Shift left first operand by the number of bits specified by the 2nd operand. E.g. (01b << 01b == 10b).                                                                                                                                             |

| >>       | Shift right first operand by the number of bits specified by the 2nd operand. E.g. $(10b >> 01b == 01b)$ .                                                                                                                                         |

#### Table 1. Arithmetic and Logic Operators

## **Processor Identification**

This section shows how to determine the processor revision.

### **Revision Determination**

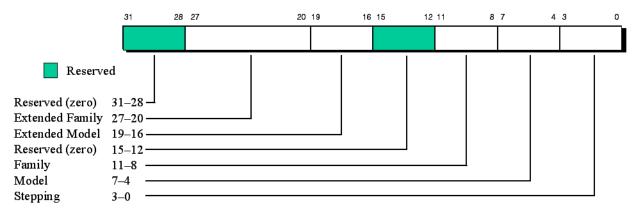

A processor revision is identified using a unique value that is returned in the EAX register after executing the CPUID instruction function 0000\_0001h (CPUID Fn0000\_0001\_EAX). Figure 1 shows the format of the value from CPUID Fn0000\_0001\_EAX. In some cases, two or more processor revisions may exist within a stepping of a processor family and are identified by a unique value in D18F4x164 Fixed Errata Register (see D18F4x164 Fixed Errata Register).

#### Figure 1. Format of CPUID Fn0000\_0001\_EAX

The following tables show the identification numbers from CPUID Fn0000\_0001\_EAX and D18F4x164 (if necessary) for each revision of the processor to each processor segment. "X" signifies that the revision has been used in the processor segment. "N/A" signifies that the revision has not been used in the processor segment.

| CPUID Fn0000_0001_EAX, D18F4x164[1:0]<br>(Mnemonic) | AMD Opteron <sup>114</sup> 6200 Series Processor | AMD Opteron <sup>114</sup> 6300 Series Processor |

|-----------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| 00600F12h, 1b (OR-B2)                               | х                                                |                                                  |

| 00600F20h, 11b (OR-C0)                              |                                                  | X                                                |

# Table 2. CPUID Values for AMD Family 15hModels 00h-0Fh G34r1 Processor Revisions

# Table 3. CPUID Values for AMD Family 15hModels 00h-0Fh C32r1 Processor Revisions

| CPUID Fn0000_0001_EAX, D18F4x164[1:0]<br>(Mnemonic) | AMD Opteron <sup>114</sup> 4200 Series Processor | AMD Opteron <sup>114</sup> 4300 Series Processor |

|-----------------------------------------------------|--------------------------------------------------|--------------------------------------------------|

| 00600F12h, 1b (OR-B2)                               | Х                                                |                                                  |

| 00600F20h, 11b (OR-C0)                              |                                                  | Х                                                |

# Table 4. CPUID Values for AMD Family 15hModels 00h-0Fh AM3r2 Processor Revisions

| CPUID Fn0000_0001_EAX, D18F4x164[1:0] | AMD FX <sup>IN</sup> Series Processor | AMD Opteron <sup>114</sup> 3200 Series Processor | AMD Opteron <sup>114</sup> 3300 Series Processor |

|---------------------------------------|---------------------------------------|--------------------------------------------------|--------------------------------------------------|

| 00600F12h, 1b (OR-B2)                 | х                                     | Х                                                |                                                  |

| 00600F20h, 11b (OR-C0)                |                                       |                                                  | Х                                                |

### D18F4x164 Fixed Errata Register

Communicating the status of an erratum within a stepping of a processor family is necessary in certain circumstances. D18F4x164 is used to communicate the status of such an erratum fix so that BIOS or system software can determine the necessity of applying the workaround. Under these circumstances, the erratum workaround references the specified bit to enable software to test for the presence of the erratum. The erratum may be specific to some steppings of the processor, and the specified bit may or may not be set on other unaffected revisions within the same family. Therefore, software should use the CPUID Fn00000\_0001\_EAX extended model, model, and stepping as the first criteria to identify the applicability of an erratum. Once defined, the definition of the status bit will persist within the family of processors.

| Bits | Description                                                                                                                                                     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | Reserved. If CPUID Fn0000_0001_EAX is 00600F12h (OR-B2), then D18F4x164 is 0000001h. If CPUID Fn0000_0001_EAX is 00600F20h (OR-C0), then D18F4x164 is 0000003h. |

### **Mixed Processor Revision Support**

AMD Family 15h processors with different revisions may be mixed in a multiprocessor system. Mixed revision support includes the AMD Opteron<sup>TM</sup> processor configurations as shown in Table 5. Processors of different package types can not be mixed in a multiprocessor system, for example a G34r1 processor can not be mixed with a C32r1 processor.

# Table 5. Supported Mixed RevisionConfigurations

| CPUID<br>Fn0000_0001_EAX<br>(Mnemonic) | 00600F12h (OR-B2) | 06000F20h (OR-C0) |

|----------------------------------------|-------------------|-------------------|

| 00600F12h (OR-B2)                      | YES               | NO                |

| 00600F20h (OR-C0)                      | NO                | YES               |

Errata workarounds must be applied according to revision as described in the Product Errata section unless otherwise noted in the workaround of an erratum.

### Programming and Displaying the Processor Name String

This section, intended for BIOS programmers, describes how to program and display the 48-character processor name string that is returned by CPUID Fn8000\_000[4:2]. The hardware or cold reset value of the processor name string is 48 ASCII NUL characters, so the BIOS must program the processor name string before any general purpose application or operating system software uses the extended functions that read the name string. It is common practice for the BIOS to display the processor name string and model number whenever it displays processor information during boot up.

*Note:* Motherboards that do not program the proper processor name string and model number will not pass AMD validation and will not be posted on the AMD Recommended Motherboard Web site.

The name string must be ASCII NUL terminated and the 48-character maximum includes that NUL character.

The processor name string is programmed by MSR writes to the six MSR addresses covered by the range MSRC001\_00[35:30]h. Refer to the *BKDG* for the format of how the 48-character processor name string maps to the 48 bytes contained in the six 64-bit registers of MSRC001\_00[35:30].

The processor name string is read by CPUID reads to a range of CPUID functions covered by CPUID Fn8000\_000[4:2]. Refer to CPUID Fn8000\_000[4:2] in the *BKDG* for the 48-character processor name string mapping to the 48 bytes contained in the twelve 32-bit registers of CPUID Fn8000\_000[4:2].

### **Constructing the Processor Name String**

This section describes how to construct the processor name string. BIOS forms the name string as follows:

- 1. If D18F5x198\_x0 is 0000000h, then use a name string of "AMD Unprogrammed Engineering Sample" and skip the remaining steps.

- 2. Read {D18F5x198\_x1, D18F5x198\_x0} and write this value to MSRC001\_0030.

- 3. Read {D18F5x198 x3, D18F5x198 x2} and write this value to MSRC001 0031.

- 4. Read {D18F5x198 x5, D18F5x198 x4} and write this value to MSRC001 0032.

- 5. Read {D18F5x198 x7, D18F5x198 x6} and write this value to MSRC001 0033.

- 6. Read {D18F5x198\_x9, D18F5x198\_x8} and write this value to MSRC001\_0034.

- 7. Read {D18F5x198\_xB, D18F5x198\_xA} and write this value to MSRC001\_0035.

# **Operating System Visible Workarounds**

This section describes how to identify operating system visible workarounds.

### MSRC001\_0140 OS Visible Work-around MSR0 (OSVW\_ID\_Length)

This register, as defined in *AMD64 Architecture Programmer's Manual Volume 2: System Programming*, order# 24593, is used to specify the number of valid status bits within the OS Visible Work-around status registers.

The reset default value of this register is 0000 0000 0000 0000h.

BIOS shall program the OSVW ID Length to 0005h prior to hand-off to the OS.

| Bits  | Description                                                   |

|-------|---------------------------------------------------------------|

| 63:16 | Reserved.                                                     |

| 15:0  | OSVW_ID_Length: OS visible work-around ID length. Read-write. |

### MSRC001\_0141 OS Visible Work-around MSR1 (OSVW\_Status)

This register, as defined in *AMD64 Architecture Programmer's Manual Volume 2: System Programming*, order# 24593, provides the status of the known OS visible errata. Known errata are assigned an OSVW\_ID corresponding to the bit position within the valid status field.

Operating system software should use MSRC001\_0140 to determine the valid length of the bit status field. For all valid status bits: 1=Hardware contains the erratum, and an OS software work-around is required or may be applied instead of a BIOS workaround. 0=Hardware has corrected the erratum, so an OS software work-around is not necessary.

The reset default value of this register is 0000 0000 0000 0000h.

| Bits | Description                                                                                                                                |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 63:5 | OsvwStatusBits: Reserved. OS visible work-around status bits. Read-write.                                                                  |  |

| 4    | <b>OsvwId4:</b> 1 = Hardware contains erratum #724, an OS workaround may be applied if available; 0 = Hardware has corrected erratum #724. |  |

| 3    | OsvwId3: Reserved, must be zero.                                                                                                           |  |

| 2    | OsvwId2: Reserved, must be zero.                                                                                                           |  |

| 1    | OsvwId1: Reserved, must be zero.                                                                                                           |  |

| 0    | OsvwId0: Reserved, must be zero.                                                                                                           |  |

BIOS shall program the state of the valid status bits as shown in Table 6 prior to hand-off to the OS.

Table 6. Cross Reference of Product Revisionto OSVW ID

| CPUID<br>Fn0000_0001_EAX<br>(Mnemonic) | MSRC001_0141 Bits    |

|----------------------------------------|----------------------|

| 00600F12h (OR-B2)                      | 0000_0000_0000_0010h |

| 00600F20h (OR-C0)                      | 0000_0000_0000_0010h |

# **Product Errata**

This section documents product errata for the processors. A unique tracking number for each erratum has been assigned within this document for user convenience in tracking the errata within specific revision levels. This table cross-references the revisions of the part to each erratum. "No fix planned" indicates that no fix is planned for current or future revisions of the processor.

Note: There may be missing errata numbers. Errata that do not affect this product family do not appear. In addition, errata that have been resolved from early revisions of the processor have been deleted, and errata that have been reconsidered may have been deleted or renumbered.

|     |                                                                                                     |                       | EAX, D18F4x164[1:0]   |  |  |

|-----|-----------------------------------------------------------------------------------------------------|-----------------------|-----------------------|--|--|

| No. | Errata Description                                                                                  | 00600F12h 01b (OR-B2) | 00600F20h 11b (OR-C0) |  |  |

| 361 | Breakpoint Due to an Instruction That Has an Interrupt Shadow May Be Lost                           | No fix j              | planned               |  |  |

| 503 | APIC Task-Priority Register May Be<br>Incorrect                                                     | No fix j              | planned               |  |  |

| 504 | Corrected L3 Errors May Lead to System<br>Hang                                                      | No fix j              | planned               |  |  |

| 505 | Scrub Rate Control Register Address<br>Depends on DctCfgSel                                         | No fix planned        |                       |  |  |

| 520 | Some Lightweight Profiling Counters Stop<br>Counting When Instruction-Based Sampling<br>is Enabled  | Х                     |                       |  |  |

| 535 | Lightweight Profiling May Not Indicate<br>Fused Branch                                              | Х                     |                       |  |  |

| 536 | Performance Counter for Instruction Cache<br>Misses Does Not Increment for Sequential<br>Prefetches | Х                     |                       |  |  |

| 537 | Performance Counter for Ineffective<br>Software Prefetches Does Not Count for L2<br>Hits            | Х                     |                       |  |  |

| 538 | Performance Counter Does Not Count for<br>Some Retired Micro-Ops                                    | Х                     |                       |  |  |

| 540 | GART Table Walk Probes May Cause<br>System Hang                                                     | No fix j              | planned               |  |  |

| 550 | Latency Performance Counters Are Not<br>Accurate                                                    | No fix j              | planned               |  |  |

| 585 | Incorrect Memory Controller Operation Due<br>to a WrDatGrossDly Setting of 3.5<br>MEMCLKs           | No fix j              | planned               |  |  |

| 586 | A Far Control Transfer Changing Processor<br>Operating Mode May Generate a False<br>Machine Check   | Х                     |                       |  |  |

|--|

|     |                                                                                                  | CPUID Fn0000_0001_EAX, D18F4x164[1:0] |                       |  |  |  |  |  |

|-----|--------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|--|--|--|--|--|

| No. | Errata Description                                                                               | 00600F12h 01b (OR-B2)                 | 00600F20h 11b (OR-C0) |  |  |  |  |  |

| 592 | VPEXTRQ and VPINSRQ May Not Signal<br>Invalid-Opcode Exception                                   | Х                                     |                       |  |  |  |  |  |

| 593 | Last-Branch Record Enabled May Cause<br>Machine Check and Incorrect<br>LastBranchToIp            | Х                                     |                       |  |  |  |  |  |

| 600 | HyperTransport <sup>™</sup> Link Retry Due to Partial<br>CRC Error May Cause System Hang         | Х                                     |                       |  |  |  |  |  |

| 602 | HyperTransport <sup>™</sup> Link Frequency Changes<br>May Cause a System Hang                    | No fix j                              | planned               |  |  |  |  |  |

| 608 | P-state Limit Changes May Not Generate<br>Interrupts                                             | No fix ]                              | planned               |  |  |  |  |  |

| 619 | Non-Posted Reads May Block Write<br>Dependent on Probe Responses                                 | Х                                     |                       |  |  |  |  |  |

| 623 | Small Code Segment Limits May Cause<br>Incorrect Limit Faults                                    | Х                                     |                       |  |  |  |  |  |

| 624 | SB-RMI Processor State Accesses May<br>Persistently Timeout if Interrupted by a<br>Warm Reset    | Х                                     |                       |  |  |  |  |  |

| 625 | SB-RMI Writes May Not Be Observed by Processor                                                   | No fix planned                        |                       |  |  |  |  |  |

| 636 | Instruction Addresses Near Canonical<br>Address Limit May Cause #GP Exception                    | Х                                     |                       |  |  |  |  |  |

| 637 | Processor Does Not Report the Correct<br>DRAM Address for MCA Errors Within the<br>CC6 Save Area | No fix j                              | planned               |  |  |  |  |  |

| 657 | MC1_STATUS Enable Bit Not Set When Logging Corrected Errors                                      | No fix j                              | planned               |  |  |  |  |  |

| 658 | CPUID Incorrectly Reports Large Page<br>Support in L2 Instruction TLB                            | Х                                     |                       |  |  |  |  |  |

| 659 | VMCB Interrupt Shadow Status May Be<br>Incorrect                                                 | Х                                     |                       |  |  |  |  |  |

| 660 | APERF May Increase Unpredictably                                                                 | Х                                     |                       |  |  |  |  |  |

| 661 | P-State Limit and Stop Clock Assertion<br>May Cause System Hang                                  | No fix                                | planned               |  |  |  |  |  |

| 663 | Local Interrupts LINT0/LINT1 May Occur<br>While APIC is Software Disabled                        | No fix j                              | planned               |  |  |  |  |  |

| 667 | Processor May Generate Incorrect P-state<br>Limit Interrupts                                     | No fix                                | planned               |  |  |  |  |  |

| 668 | Load Operation May Receive Incorrect Data<br>After Floating-point Exception                      | Х                                     |                       |  |  |  |  |  |

| 671 | Debug Breakpoint on Misaligned Store May<br>Cause System Hang                                    | Х                                     |                       |  |  |  |  |  |

#### Table 7. Cross-Reference of Processor Revision to Errata (continued)

|     |                                                                                                    | CPUID Fn0000_0001_EAX, D18F4x164[1:0] |                       |  |  |  |

|-----|----------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|--|--|--|

| No. | Errata Description                                                                                 | 00600F12h 01b (OR-B2)                 | 00600F20h 11b (OR-C0) |  |  |  |

| 672 | SVM Guest Performance Counters May Be<br>Inaccurate Due to SMI                                     | Х                                     |                       |  |  |  |

| 673 | Misaligned Page Crossing String Operations<br>May Cause System Hang                                | Х                                     |                       |  |  |  |

| 674 | Processor May Cache Prefetched Data from<br>Remapped Memory Region                                 | Х                                     |                       |  |  |  |

| 675 | Instructions Performing Read-Modify-Write<br>May Alter Architectural State Before #PF              | Х                                     |                       |  |  |  |

| 685 | Some Processor Cores May Have Inaccurate<br>Instruction Cache Fetch Performance<br>Counter         |                                       | Х                     |  |  |  |

| 689 | AM3r2 Six Core Processor May Limit P-<br>State When Core C6 State Is Disabled                      | Х                                     |                       |  |  |  |

| 690 | Northbridge FIFO Read/Write Pointer<br>Overlap May Cause Hang or Protocol Error<br>Machine Check   | No fix j                              | planned               |  |  |  |

| 691 | Processors Using 1 MB L3 Subcaches May<br>Execute a Write-Back Invalidate Operation<br>Incorrectly | No fix planned                        |                       |  |  |  |

| 693 | Performance Counter May Incorrectly<br>Count MXCSR Loads                                           | No fix j                              | planned               |  |  |  |

| 694 | IBS Sampling of Instruction Fetches May<br>Be Uneven                                               | No fix j                              | planned               |  |  |  |

| 695 | Processor May Interpret FCW Incorrectly<br>after FNSAVE/FSAVE Limit Fault                          | No fix j                              | planned               |  |  |  |

| 699 | Processor May Generate Illegal Access in VMLOAD or VMSAVE Instruction                              |                                       | Х                     |  |  |  |

| 704 | Processor May Report Incorrect Instruction<br>Pointer                                              |                                       | Х                     |  |  |  |

| 707 | Performance Counter for Locked<br>Operations May Count Cycles from Non-<br>Locked Operations       |                                       | Х                     |  |  |  |

| 708 | Initial Value of Time Stamp Counter May<br>Include an Offset Error                                 |                                       | Х                     |  |  |  |

| 709 | Processor May Be Limited to Minimum P-<br>state After a P-state Limit Change                       | No fix planned                        |                       |  |  |  |

| 714 | Processor May Check DRAM Address<br>Maps While Using L2 Cache as General<br>Storage during Boot    | No fix planned                        |                       |  |  |  |

| 717 | Instruction-Based Sampling May Be<br>Inaccurate                                                    | Х                                     |                       |  |  |  |

| 718 | Instruction-Based Sampling May Be<br>Inaccurate                                                    | No fix j                              | planned               |  |  |  |

#### Table 7. Cross-Reference of Processor Revision to Errata (continued)

|     |                                                                                                        | CPUID Fn0000_0001_EAX, D18F4x164[1:0] |                       |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------|--|--|--|

| No. | Errata Description                                                                                     | 00600F12h 01b (OR-B2)                 | 00600F20h 11b (OR-C0) |  |  |  |

| 719 | Instruction-Based Sampling Fetch Counter<br>Always Starts at Maximum Value                             | No fix                                | planned               |  |  |  |

| 720 | Processor May Not Respect Interrupt<br>Shadow                                                          | No fix                                | planned               |  |  |  |

| 724 | Unintercepted Halt Instruction May Cause<br>Protocol Machine Check or Unpredictable<br>System Behavior | No fix                                | planned               |  |  |  |

| 725 | Incorrect APIC Remote Read Behavior                                                                    | No fix                                | planned               |  |  |  |

| 726 | Processor May Report Incorrect MCA<br>Address for Loads that Cross Address<br>Boundaries               | No fix j                              | planned               |  |  |  |

| 727 | Processor Core May Hang During CC6<br>Resume                                                           |                                       | Х                     |  |  |  |

| 734 | Processor May Incorrectly Store VMCB<br>Data                                                           |                                       | Х                     |  |  |  |

| 737 | Processor Does Not Check 128-bit<br>Canonical Address Boundary Case on<br>Logical Address              | No fix                                | planned               |  |  |  |

| 739 | Processor May Read Branch Status Register<br>With Inconsistent Parity Bit                              |                                       | Х                     |  |  |  |

| 740 | Lightweight Profiling May Cause System<br>Hang with Concurrent Stop Clock                              | No fix                                | planned               |  |  |  |

| 742 | DRAM Scrub Request During Register<br>Write May Cause Unpredictable Behavior                           | No fix                                | planned               |  |  |  |

| 744 | Processor CC6 May Not Restore Trap<br>Registers                                                        | No fix                                | planned               |  |  |  |

| 745 | Processor May Incorrectly Report Cache<br>Sharing Property in CPUID Topology                           | Х                                     |                       |  |  |  |

| 775 | Processor May Present More Than One<br>#DB Exception on REP-INS or REP-OUTS<br>Instructions            | No fix                                | planned               |  |  |  |

| 778 | Processor Core Time Stamp Counters May<br>Experience Drift                                             | No fix                                | planned               |  |  |  |

| 786 | APIC Timer Periodic Mode is Imprecise                                                                  | No fix                                | planned               |  |  |  |

| 815 | Processor May Read Partially Updated<br>Branch Status Register                                         |                                       | х                     |  |  |  |

# **Cross-Reference of Errata to Package Type**

This table cross-references the errata to each package type. "X" signifies that the erratum applies to the package type. An empty cell signifies that the erratum does not apply. An erratum may not apply to a package type due to a specific characteristic of the erratum, or it may be due to the affected silicon revision(s) not being used in this package.

| Table 8. Cross-Reference  |

|---------------------------|

| of Errata to Package Type |

|        | Package |       |       |  |  |  |

|--------|---------|-------|-------|--|--|--|

| Errata | AM3r2   | C32r1 | G34r1 |  |  |  |

| 361    | Х       | Х     | Х     |  |  |  |

| 503    | Х       | Х     | Х     |  |  |  |

| 504    | Х       | Х     | Х     |  |  |  |

| 505    | Х       | Х     | Х     |  |  |  |

| 520    | Х       | Х     | Х     |  |  |  |

| 535    | Х       | Х     | Х     |  |  |  |

| 536    | Х       | Х     | Х     |  |  |  |

| 537    | Х       | Х     | Х     |  |  |  |

| 538    | Х       | Х     | Х     |  |  |  |

| 540    | Х       | Х     | Х     |  |  |  |

| 550    | Х       | Х     | Х     |  |  |  |

| 585    | Х       | Х     | Х     |  |  |  |

| 586    | Х       | Х     | Х     |  |  |  |

| 592    | Х       | Х     | Х     |  |  |  |

| 593    | Х       | Х     | Х     |  |  |  |

| 600    |         | Х     | Х     |  |  |  |

| 602    | Х       | Х     | Х     |  |  |  |

| 608    | Х       | Х     | Х     |  |  |  |

| 619    | Х       | Х     | Х     |  |  |  |

| 623    | Х       | Х     | Х     |  |  |  |

| 624    | Х       | Х     | Х     |  |  |  |

| 625    | Х       | Х     | Х     |  |  |  |

| 636    | Х       | Х     | Х     |  |  |  |

| 637    | Х       | Х     | Х     |  |  |  |

| 657    | Х       | Х     | Х     |  |  |  |

| 658    | Х       | Х     | Х     |  |  |  |

| 659    | Х       | Х     | Х     |  |  |  |

| 660    | Х       | Х     | Х     |  |  |  |

| 661    | Х       | Х     | Х     |  |  |  |

| 663    | Х       | Х     | Х     |  |  |  |

# Table 8. Cross-Referenceof Errata to Package Type(continued)

|        |       | Package |       |

|--------|-------|---------|-------|

| Errata | AM3r2 | C32r1   | G34r1 |

| 667    | Х     | Х       | Х     |

| 668    | Х     | Х       | Х     |

| 671    | Х     | Х       | Х     |

| 672    | Х     | Х       | Х     |

| 673    | Х     | Х       | Х     |

| 674    | Х     | Х       | Х     |

| 675    | Х     | Х       | Х     |

| 685    | Х     | Х       | Х     |

| 689    | Х     |         |       |

| 690    | Х     | Х       | Х     |

| 691    | Х     |         |       |

| 693    | Х     | Х       | Х     |

| 694    | Х     | Х       | Х     |

| 695    | Х     | Х       | Х     |

| 699    | Х     | Х       | Х     |

| 704    | Х     | Х       | Х     |

| 707    | Х     | Х       | Х     |

| 708    | Х     | Х       | Х     |

| 709    | Х     | Х       | Х     |

| 714    | Х     | Х       | Х     |

| 717    | Х     | Х       | Х     |

| 718    | Х     | Х       | Х     |

| 719    | Х     | Х       | Х     |

| 720    | Х     | Х       | Х     |

| 724    | Х     | Х       | Х     |

| 725    | Х     | Х       | Х     |

| 726    | Х     | Х       | Х     |

| 727    | Х     | Х       | Х     |

| 734    | Х     | Х       | Х     |

| 737    | Х     | Х       | Х     |

| 739    | Х     | Х       | Х     |

| 740    | Х     | Х       | Х     |

| 742    | Х     | Х       | Х     |

| 744    | Х     |         | Х     |

| 745    | Х     |         |       |

Revision Guide for AMD Family 15h Models 00h-0Fh Processors

48063 Rev. 3.24 September 2014

# Table 8. Cross-Referenceof Errata to Package Type(continued)

|        | Package |       |       |  |  |  |

|--------|---------|-------|-------|--|--|--|

| Errata | AM3r2   | C32r1 | G34r1 |  |  |  |

| 759    | Х       | Х     | Х     |  |  |  |

| 775    | Х       | Х     | Х     |  |  |  |

| 778    | Х       | Х     | Х     |  |  |  |

| 786    | Х       | Х     | Х     |  |  |  |

| 815    |         |       | Х     |  |  |  |

# **Cross-Reference of Errata to Processor Segments**

This table cross-references the errata to each processor segment. "X" signifies that the erratum applies to the processor segment. An empty cell signifies that the erratum does not apply. An erratum may not apply to a processor segment due to a specific characteristic of the erratum, or it may be due to the affected silicon revision(s) not being used in this processor segment.

# Table 9. Cross-Reference of Errata to Processor Segments

| Segme  |                          | Processor Segment           |                             |                             |                             |                             |                                          |  |

|--------|--------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------------------------------------------|--|

| Errata | AMD FX"-Series Processor | AMD Opteron" 3200 Processor | AMD Opteron" 3300 Processor | AMD Opteron" 4200 Processor | AMD Opteron" 4300 Processor | AMD Opteron" 6200 Processor | AMD Opteron <sup>11</sup> 6300 Processor |  |

| 361    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 503    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 504    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 505    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 520    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 535    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 536    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 537    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 538    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 540    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 550    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 585    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 586    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 592    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 593    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 600    |                          |                             |                             | Х                           |                             | Х                           |                                          |  |

| 602    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 608    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 619    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 623    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 624    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 625    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 636    | Х                        | Х                           |                             | Х                           |                             | Х                           |                                          |  |

| 637    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

| 657    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                                        |  |

# Table 9. Cross-Reference of Errata to Processor Segments (continued)

|        | Processor Segment        |                             |                             |                             |                             |                             |                             |

|--------|--------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|

| Errata | AMD FX"-Series Processor | AMD Opteron" 3200 Processor | AMD Opteron" 3300 Processor | AMD Opteron" 4200 Processor | AMD Opteron" 4300 Processor | AMD Opteron" 6200 Processor | AMD Opteron" 6300 Processor |

| 658    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 659    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 660    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 661    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 663    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 667    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 668    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 671    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 672    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 673    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 674    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 675    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 685    | Х                        |                             | Х                           |                             | Х                           |                             | Х                           |

| 689    | Х                        |                             |                             |                             |                             |                             |                             |

| 690    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 691    |                          | Х                           |                             |                             |                             |                             |                             |

| 693    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 694    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 695    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 699    | Х                        |                             | Х                           |                             | Х                           |                             | Х                           |

| 704    | Х                        |                             | Х                           |                             | Х                           |                             | Х                           |

| 707    | Х                        |                             | Х                           |                             | Х                           |                             | Х                           |

| 708    | Х                        |                             | Х                           |                             | Х                           |                             | Х                           |

| 709    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 714    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 717    | Х                        | Х                           |                             | Х                           |                             | Х                           |                             |

| 718    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 719    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 720    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 724    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

| 725    | Х                        | Х                           | Х                           | Х                           | Х                           | Х                           | Х                           |

# Table 9. Cross-Reference of Errata to ProcessorSegments (continued)

| Processor Segment |                          |                             |                             |                                          |                                          |                             |                             |

|-------------------|--------------------------|-----------------------------|-----------------------------|------------------------------------------|------------------------------------------|-----------------------------|-----------------------------|

| Errata            | AMD FX"-Series Processor | AMD Opteron" 3200 Processor | AMD Opteron" 3300 Processor | AMD Opteron <sup>11</sup> 4200 Processor | AMD Opteron <sup>11</sup> 4300 Processor | AMD Opteron" 6200 Processor | AMD Opteron" 6300 Processor |

| 726               | Х                        | Х                           | Х                           | Х                                        | Х                                        | Х                           | Х                           |

| 727               | Х                        |                             | Х                           |                                          | Х                                        |                             | Х                           |

| 734               | Х                        |                             | Х                           |                                          | Х                                        |                             | Х                           |

| 737               | Х                        | Х                           | Х                           | Х                                        | Х                                        | Х                           | Х                           |

| 739               | Х                        |                             | Х                           |                                          | Х                                        |                             | Х                           |

| 740               | Х                        | Х                           | Х                           | Х                                        | Х                                        | Х                           | Х                           |

| 742               | Х                        | Х                           | Х                           | Х                                        | Х                                        | Х                           | Х                           |

| 744               | Х                        |                             |                             |                                          |                                          |                             | Х                           |

| 745               | Х                        |                             |                             |                                          |                                          |                             |                             |

| 759               | Х                        | Х                           |                             | Х                                        |                                          | Х                           |                             |

| 775               | Х                        | Х                           | Х                           | Х                                        | Х                                        | Х                           | Х                           |

| 778               | Х                        | Х                           | Х                           | Х                                        | Х                                        | Х                           | Х                           |

| 786               | Х                        | Х                           | Х                           | Х                                        | Х                                        | Х                           | Х                           |

| 815               |                          |                             |                             |                                          |                                          |                             | Х                           |

### 361 Breakpoint Due to an Instruction That Has an Interrupt Shadow May Be Lost

### Description

A #DB exception occurring in guest mode may be discarded under the following conditions:

- A trap-type #DB exception is generated in guest mode during execution of an instruction with an interrupt shadow, and

- The instruction that generated the exception is immediately followed by an instruction resulting in #VMEXIT.

### **Potential Effect on System**

None expected under normal conditions. Debug exceptions may not be received for programs running under a hypervisor.

#### Suggested Workaround

None.

### Fix Planned

## 503 APIC Task-Priority Register May Be Incorrect

#### Description

An APIC task priority register (TPR) write may use an incorrect internal buffer for the data.

#### **Potential Effect on System**

Incorrect interrupt prioritization.

#### Suggested Workaround

BIOS should set MSRC001\_102A[11] to 1b.

#### **Fix Planned**

# 504 Corrected L3 Errors May Lead to System Hang

#### Description

Under a highly specific and detailed set of internal timing conditions that involves corrected L3 errors, a processor read from the L3 cache may hang.

#### **Potential Effect on System**

System hang.

#### Suggested Workaround

BIOS should program D18F3x1B8[18] to 1b.

#### **Fix Planned**

#### Description

When DCT Configuration Select[DctCfgSel] (D18F1x10C[0]) is 1b, accesses to the Scrub Rate Control register (D18F3x58) incorrectly accesses a different register that does not actually affect any hardware.

#### **Potential Effect on System**

Incorrect scrub rate controls may be read or in effect.

#### Suggested Workaround

Software should clear DctCfgSel (D18F1x10C[0]) to 0b prior to any access to D18F3x58 Scrub Rate Control Register. The software must serialize any accesses to D18F3x58 with other accesses to registers that use DctCfgSel.

When enabling scrub settings, BIOS should write D18F3x58 twice with the same value - once with D18F1x10C[0] set to 0b and once with D18F1x10C[0] set to 1b.

BIOS should program D18F1x10C[0] to 0b before handing over control to the operating system.

#### Fix Planned

### 520 Some Lightweight Profiling Counters Stop Counting When Instruction-Based Sampling is Enabled

### Description

When Lightweight Profiling (LWP) and Instruction-Based Sampling (IBS) measurement of instruction execution are simultaneously enabled, the following LWP counters do not increment:

- Instructions retired event counter (LWP EventId 2)

- Branches retired event counter (LWP EventId 3)

LWP is enabled once software executes a LLWCP or XRSTOR instruction with a valid LWPCB address. IBS instruction execution sampling is enabled when IBS Execution Control[IbsOpEn] (MSRC001\_1033[17]) is 1b.

### **Potential Effect on System**

Performance monitoring software using LWP may not have a count of instructions retired or branches retired.

#### Suggested Workaround

None.

#### **Fix Planned**

# 535 Lightweight Profiling May Not Indicate Fused Branch

#### Description

The Lightweight Profiling (LWP) fused operation bit (FUS - bit 28 of the branch retired event record, LWP EventId 3) may not be set when the processor core is profiling a fused branch (a compare operation followed by a conditional branch that is executed as a single operation internally) and a #PF or nested-paging exception occurs during the storing of the event.

#### **Potential Effect on System**

Performance monitoring software may not profile a fused branch correctly.

#### Suggested Workaround

None.

#### **Fix Planned**

### 536 Performance Counter for Instruction Cache Misses Does Not Increment for Sequential Prefetches

### Description

PMCx081 (Instruction Cache Misses) does not increment for L1 instruction cache misses that are due to sequential prefetches.

#### **Potential Effect on System**

Performance monitoring software may undercount instruction cache misses.

#### **Suggested Workaround**

Performance monitoring software may use the difference of PMCx083 and PMCx082 as a close approximation of instruction cache misses.

#### Fix Planned

### 537 Performance Counter for Ineffective Software Prefetches Does Not Count for L2 Hits

#### Description

PMCx052[3] (ineffective software prefetch due to an L2 cache hit) does not increment.

#### **Potential Effect on System**

Performance monitoring software can not determine ineffective software prefetches due to an L2 cache hit.

#### Suggested Workaround

None.

#### **Fix Planned**

### 538 Performance Counter Does Not Count for Some Retired Micro-Ops

### Description

Some instructions with F0h in the opcode byte are incorrectly detected by the processor core as empty microops, causing the processor core to not properly increment PMCx0C1.

The following instructions may cause this performance monitor to undercount:

- FCOMI

- FCOMIP

- F2XM1

#### **Potential Effect on System**

Performance monitoring software will not have an accurate count of retired micro-ops. The performance counter may undercount and the error is directly proportional to the number of the instructions listed above.

#### Suggested Workaround

None.

#### **Fix Planned**

#### Description

Probes that are generated for GART table walks may overflow internal queues and lead to a deadlock.

#### **Potential Effect on System**

System hang.

#### Suggested Workaround

System software that initializes the GART Table Base Address (D18F3x98) should set GART Aperture Control[DisGartTblWlkPrb] (D18F3x90[6]) = 1b. The GART tables should be in UC DRAM or be updated only using strongly-ordered uncacheable writes.

System software should not set HWCR[ForceRdWrSzPrb] (MSRC001 0015[23]) if GART is enabled.

#### **Fix Planned**

# **550 Latency Performance Counters Are Not Accurate**

#### Description

Latency performance counters NBPMCx1E2 through NBPMCx1E7 are not accurate when L3 speculative miss prefetching is enabled (D18F2x1B0[13] = 0b, Extended Memory Controller Configuration Low[SpecPrefDis]).

#### **Potential Effect on System**

Performance monitoring software cannot accurately measure latency events. The reported latency may greatly exceed the actual latency in some instances.

#### **Suggested Workaround**

No workaround is recommended.

Performance monitoring software may set D18F2x1B0[13] = 1b to collect accurate latency values. This workaround has an impact to overall system performance.

#### **Fix Planned**

### 585 Incorrect Memory Controller Operation Due to a WrDatGrossDly Setting of 3.5 MEMCLKs

#### Description

The memory controller may incorrectly issue a ZQ command during a 64-byte write operation when WrDatGrossDly is set to a value of 3.5 MEMCLKs (111b).

#### **Potential Effect on System**

Undefined system behavior.

#### **Suggested Workaround**

If WrDatGrossDly (D18F2x9C\_x0000\_0[3:0]0[3:1]\_dct[1:0]) for all byte lanes (including the ECC byte lane) and all populated DIMMs = 111b, BIOS should set DataTxFifoWrDly (D18F2x210\_dct[1:0]\_nbp[3:0] bits 18:16) as specified in the *BIOS and Kernel Developer's Guide (BKDG) for AMD Family 15h Models 00h-0Fh Processors*, order# 42301, but with a minimum value of 010b.

#### **Fix Planned**

### 586 A Far Control Transfer Changing Processor Operating Mode May Generate a False Machine Check

### Description

A far control transfer that changes the processor operating mode may erroneously indicate a decoder instruction buffer parity error (DEIBP) machine check, leading to a system shutdown. The extended error code logged in the IF Machine Check Status register indicates a decode instruction buffer error (MSR0000\_0405[20:16] = 10010b).

#### **Potential Effect on System**