# **BGA Breakouts and Routing**

Second edition

**Charles Pfeil**

## **BGA Breakouts and Routing**

## Effective Design Methods for Very Large BGAs

Second Edition Version 5.0

#### Charles Pfeil 8/26/2008

Very large BGAs, over 1500 pins, present a unique challenge for routing on a printed circuit board. Often just routing out of the BGA is the primary contributor to the number of layers required for routing. This book presents a number of studies and solutions for addressing these challenges. WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either expressed or implied.

This document is for information and instruction purposes. Mentor Graphics reserves the right to make changes in specifications and other information contained in this publication without prior notice, and the reader should, in all cases, consult Mentor Graphics to determine whether any changes have been made.

#### **Contractor is:**

Mentor Graphics Corporation 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777 Telephone: 503.685.7000 Toll-Free Telephone: 800.592.2210 Website: www.mentor.com SupportNet: www.mentor.com/supportnet

Contact the author: charles\_pfeil@mentor.com

**TRADEMARKS:** The trademarks, logos and service marks ("Marks") used herein are the property of Mentor Graphics Corporation or other third parties. No one is permitted to use these Marks without the prior written consent of Mentor Graphics or the respective third-party owner. A current list of Mentor Graphics' trademarks may be viewed at: www.mentor.com/terms\_conditions/trademarks.cfm

© Copyright 2008 Mentor Graphics Corporation. All Rights Reserved.

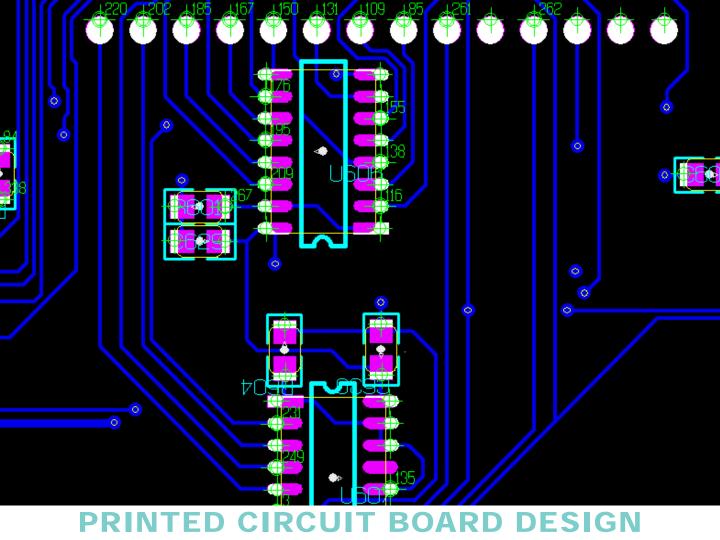

### **PRINTED CIRCUIT BOARD DESIGN**

Who could have possibly imagined that significant inventions created by the great minds of yesterday would parlay into the groundbreaking visions of today's intricate technology? Because of risk takers of only a few decades ago, today's designers, enabled by Mentor Graphics' innovative PCB design solutions are inventing products that improve effectiveness and efficiency resulting in improved productivity.

To connect with other innovators and visionaries of future electronic development join Mentor's PCB community at <u>http://communities.mentor.com/mgcx/index.jspa,</u> call us at 800.547.3000 or for more information visit <u>www.mentor.com/pcb</u>

#### Acknowledgments

I gratefully acknowledge those who contributed material, ideas, and review during the production of this book.

• My colleagues at Mentor Graphics who provided review, discussion and feedback on various aspects of the content:

Happy Holden Steve Kaufer Chuck Ferry Kendall Hiles

• Mentor Graphics SDD customers who took the time to meet with me and discuss the issues:

Vern Wnek and Kevin Seaman, Broadcom Aydin Cokoyoglu, Alcatel-Lucent Shaun Olsen, Intel Kathy Brady, Raytheon Larry Paul and Andy Green, Qualcomm

- The software and package design team at Xilinx who provide feedback on my research with the Virtex-4 and Virtex-5 devices.

- The Marcom team at Mentor Graphics who provided review and produced the finished copy: Leslie Van Grove Mark Forbes

Thanks to everyone who supported and encouraged this effort.

## **Table of Contents**

| Preface – Second Edition                                                                                                                                                                                                           | v                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Chapter One - Introduction                                                                                                                                                                                                         | 1                                                                          |

| Expedition PCB                                                                                                                                                                                                                     | 2                                                                          |

| Figures                                                                                                                                                                                                                            | 2                                                                          |

| Definitions                                                                                                                                                                                                                        | 2                                                                          |

| Via Types                                                                                                                                                                                                                          | 6                                                                          |

| Stackup Types                                                                                                                                                                                                                      | 6                                                                          |

| The Problem                                                                                                                                                                                                                        | 12                                                                         |

| Solutions                                                                                                                                                                                                                          | 15                                                                         |

| Chapter Two - BGA Packages                                                                                                                                                                                                         | 17                                                                         |

| High Pin Counts                                                                                                                                                                                                                    | 17                                                                         |

| Impact on Routing, Performance and Cost                                                                                                                                                                                            | 20                                                                         |

| Off-Matrix Ball Pads                                                                                                                                                                                                               | 22                                                                         |

| 0.8mm Pin-Pitch                                                                                                                                                                                                                    | 23                                                                         |

| The Near Future                                                                                                                                                                                                                    | 24                                                                         |

|                                                                                                                                                                                                                                    | 25                                                                         |

| Chapter Three - HDI Layer Stackups                                                                                                                                                                                                 | 25                                                                         |

| Fabrication Vendors                                                                                                                                                                                                                |                                                                            |

| • • •                                                                                                                                                                                                                              | 25                                                                         |

| Fabrication Vendors                                                                                                                                                                                                                | 25<br>26                                                                   |

| Fabrication Vendors<br>Dependencies                                                                                                                                                                                                | 25<br>26<br>27                                                             |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types                                                                                                                                                                   | 25<br>26<br>27<br>31                                                       |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details                                                                                                                                            | 25<br>26<br>27<br>31<br>36                                                 |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details<br>Via Models                                                                                                                              | 25<br>26<br>27<br>31<br>36<br>39                                           |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details<br>Via Models<br>Plane Layer Assignments.                                                                                                  | 25<br>26<br>27<br>31<br>36<br>39<br>42                                     |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details<br>Via Models<br>Plane Layer Assignments<br>Layer Count                                                                                    | 25<br>26<br>27<br>31<br>36<br>39<br>42<br>43                               |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details<br>Via Models<br>Plane Layer Assignments<br>Layer Count<br>Design Rules                                                                    | 25<br>26<br>27<br>31<br>36<br>39<br>42<br>43<br>43                         |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details<br>Via Models<br>Plane Layer Assignments<br>Layer Count<br>Design Rules<br>Fanout Patterns                                                 | 25<br>26<br>27<br>31<br>36<br>39<br>42<br>43<br>43<br>43<br>44             |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details<br>Via Models<br>Plane Layer Assignments<br>Layer Count<br>Design Rules<br>Fanout Patterns<br>Signal Integrity                             | 25<br>26<br>27<br>31<br>36<br>39<br>42<br>43<br>43<br>43<br>44<br>44       |

| Fabrication Vendors<br>Dependencies<br>Overview of Stackup Types<br>HDI Stackup Details<br>Via Models<br>Plane Layer Assignments<br>Layer Count<br>Design Rules<br>Fanout Patterns<br>Signal Integrity<br>Recommended HDI Stackups | 25<br>26<br>27<br>31<br>36<br>39<br>42<br>43<br>43<br>43<br>44<br>44<br>44 |

| Chapter Four - Fanout Patterns                      | 55  |

|-----------------------------------------------------|-----|

| Theoretical Breakout Methods                        | 56  |

| Signal Integrity Concerns                           | 60  |

| Minimizing the Variables                            | 61  |

| Fanout Pattern Goals and Approach                   | 64  |

| Through-Vias                                        | 65  |

| Drilled Blind and Buried-vias                       | 78  |

| HDI Micro-Vias                                      | 89  |

| Summary                                             | 94  |

| Chapter Five - Layer Biased Breakouts               | 95  |

| Board Description                                   | 95  |

| General Assessment of Original Board                | 95  |

| Recommendations and Solutions                       | 96  |

| Using Layer Biased Breakouts                        | 97  |

| Fanouts for Micro-Via Layers                        | 101 |

| Route Results                                       | 119 |

| Summary                                             | 120 |

| Chapter Six - 0.8mm Pin-Pitch BGA Tests             | 121 |

| Test Scenario                                       | 121 |

| Test 1: Through-Vias                                | 124 |

| Test 2: Micro-Vias and Through-Vias                 | 134 |

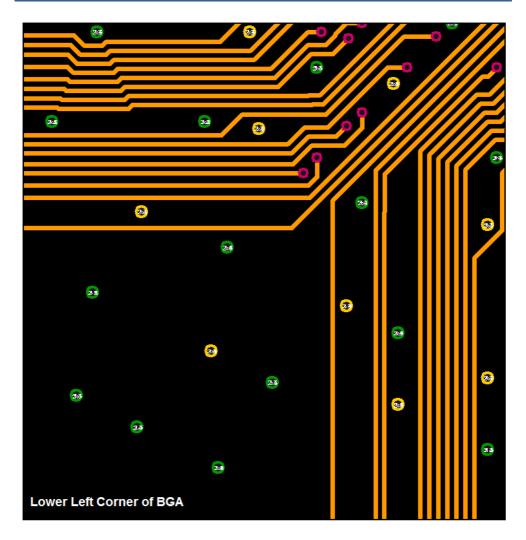

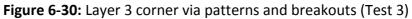

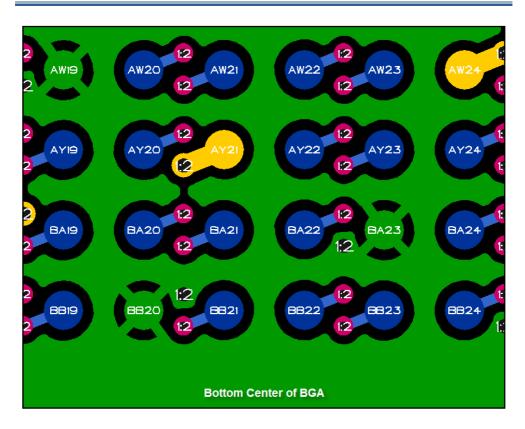

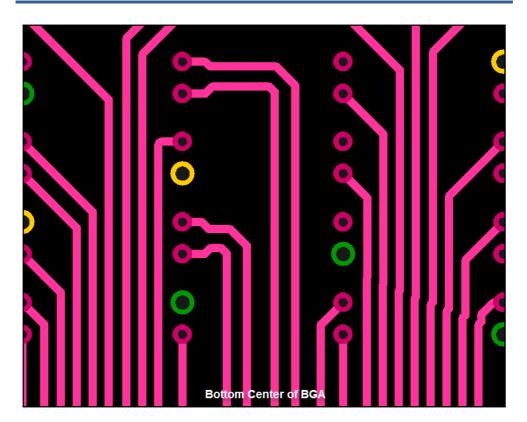

| Test 3: Any-Layer-Vias                              |     |

| Summary                                             | 163 |

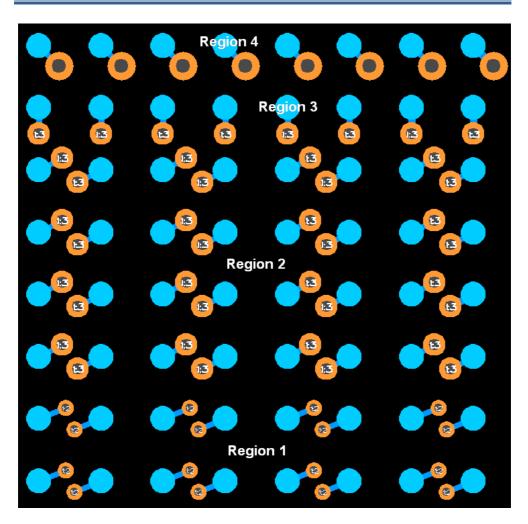

| Chapter Seven - Software for Generating BGA Fanouts | 165 |

| Method                                              | 166 |

| Regions                                             | 167 |

| Adding Blind and Through-Vias                       | 168 |

| Adding Buried Vias                                  | 170 |

| Additional Example                                  | 173 |

| Conclusion                                          | 175 |

| About the Author                                    | 177 |

#### **Preface – Second Edition**

This new edition includes updates throughout the book with greater details, new methods, and clearer figures. It also has an additional chapter called "Software for Generating BGA Fanouts". This chapter describes how to use new software in Mentor Graphics Expedition PCB and BoardStationXE to automatically generate efficient fanouts patterns for large dense BGAs.

#### **Chapter One - Introduction**

This book is for PCB designers who are designing boards with multiple very large Ball Grid Array (BGA) packages. It explores the impact of dense BGAs with high pin-count on PCB design and provides solutions for the inherent design challenges. Though you may not yet have been confronted with the difficulties of routing BGAs and the impact on fabrication costs and signal integrity, this book will reveal these potential pitfalls as well as methods to mitigate these problems.

There are volumes of information about BGA package technology that look at the device from all aspects including materials, thermal characteristics, assembly methods, reliability, and electrical performance; yet little guidance is available regarding effective PCB design methods.

The BGA is the most popular packaging option at this time for large pin count devices. Used for many circuit technologies including FPGA, SoC, SiP and ASIC, the BGA provides a cost-effective and reliable method to mount the device on a printed circuit board. There are many benefits to using this package; however, its greatest asset - the ability to provide an extremely dense array of thousands of pins - also turns out to be a tremendous problem for PCB design.

The BGA density and pin count continues to increase; yet, the ability to effectively design with these devices has not kept pace. Fortunately significant advancements in PCB fabrication technology have enabled further miniaturization in the manufacturing process. These improvements along with new software and design methods specifically for BGAs provide a means to successfully design using these devices.

The intent with this book is to provide PCB designers with knowledge and proven techniques that may be used to overcome the challenges presented by current and future BGA devices. These techniques have been developed

over the last 18 months and have come from extensive evaluation of various BGA packages and real PCB designs.

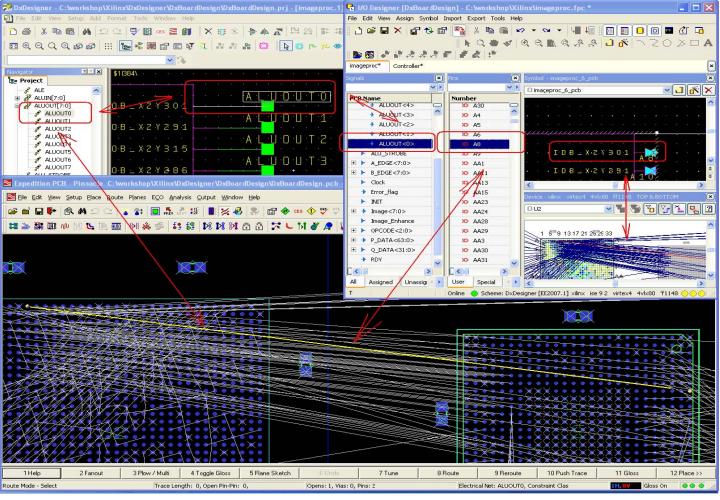

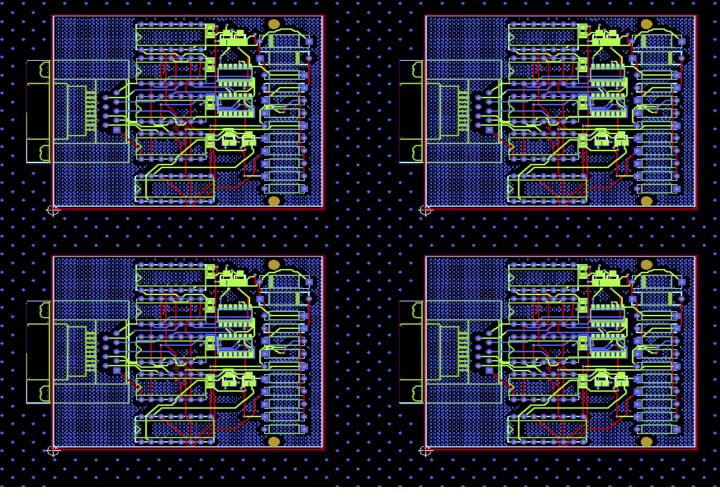

#### **Expedition PCB**

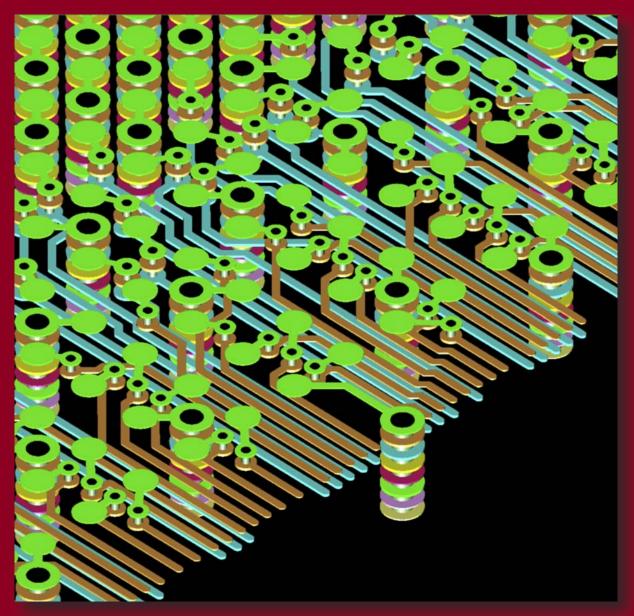

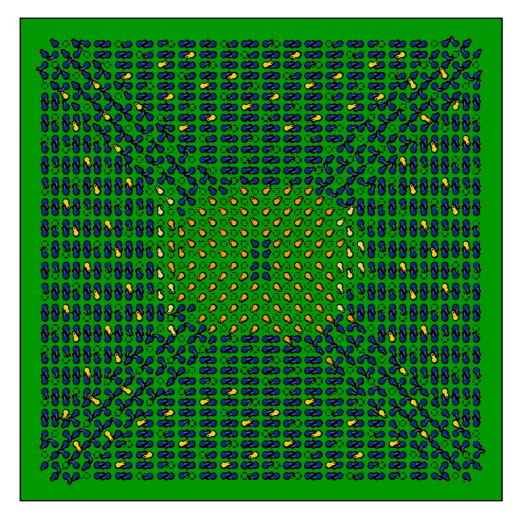

All the figures showing PCB design graphics are screen captures from Mentor Graphics Expedition<sup>TM</sup> PCB. The cover image was created using the prototype Expedition PCB 3D Viewer. The fanouts were created using the existing fanout and copy trace routines, and the escape traces were mostly added using prototype automatic routing software. These capabilities and more related to BGA breakouts and routing are available in the 2007.3 release of Mentor's Expedition PCB and Board Station<sup>®</sup> XE suite of tools.

#### Figures

There are more than a hundred figures in this book showing details about BGA breakouts. I encourage you to study them with the intent of finding techniques and tricks that will help you route these challenging devices. With all the variables involved in routing of large BGAs, my specific examples may not map directly to your experiences; however, you should be able to discover principles that can, at a minimum, give you some new ideas that will enable greater route density, a reduction in layer count and help bring your products to market faster.

#### Definitions

These definitions are in the context of BGA breakouts and routing.

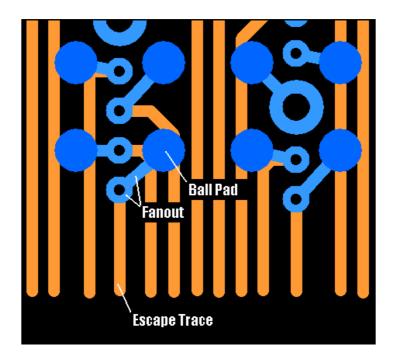

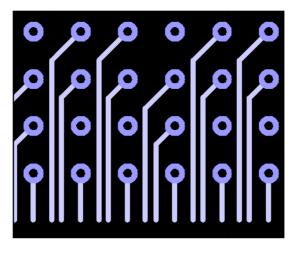

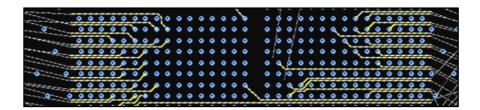

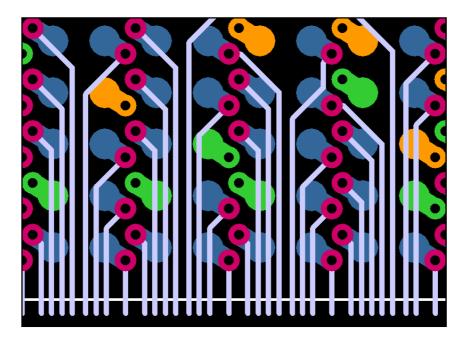

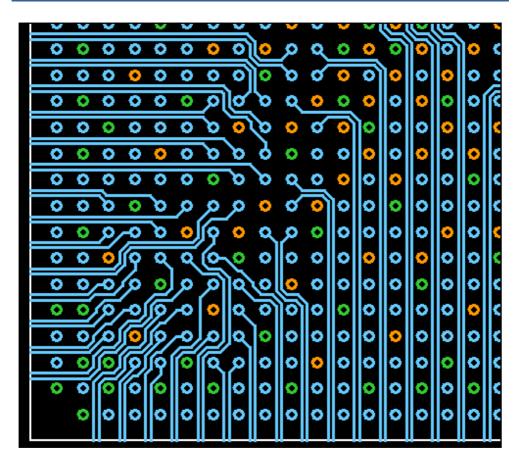

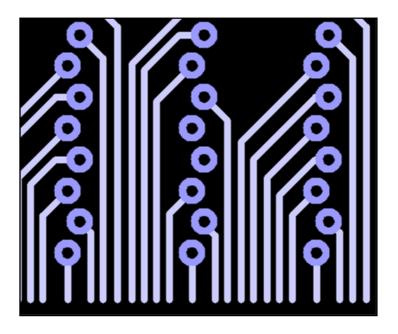

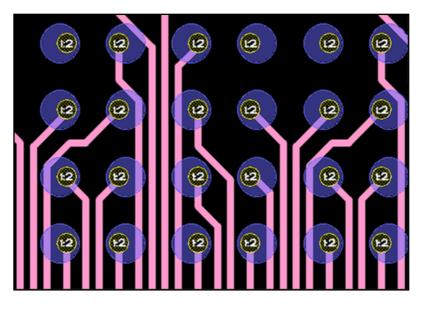

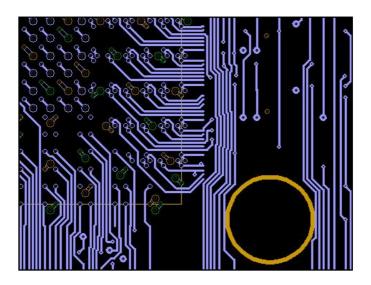

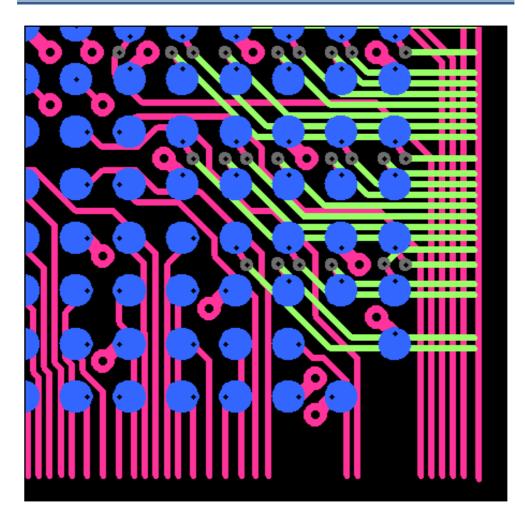

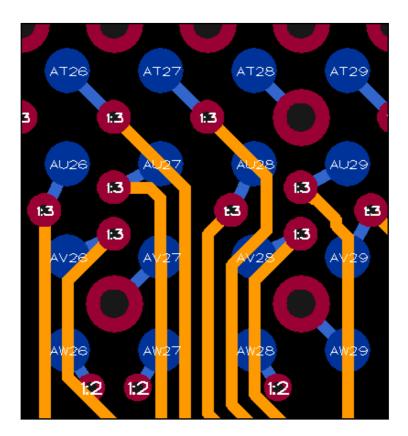

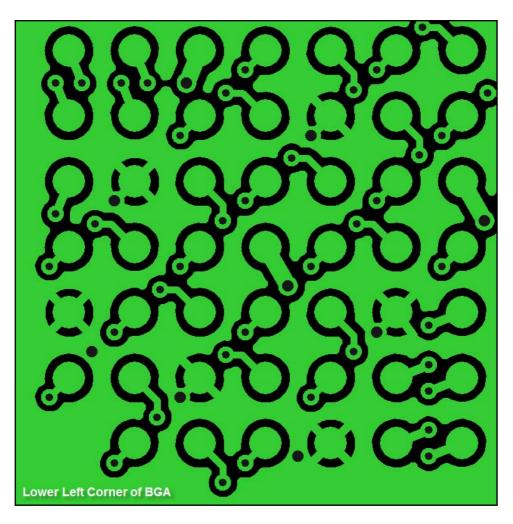

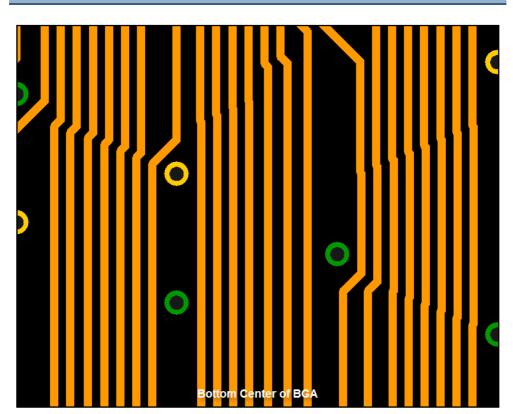

**Breakout** - The combination of fanouts and escape traces, which allow routing out of the BGA pin array to the perimeter of the device prior to general routing of the PCB. See figures 1-1 and 1-2.

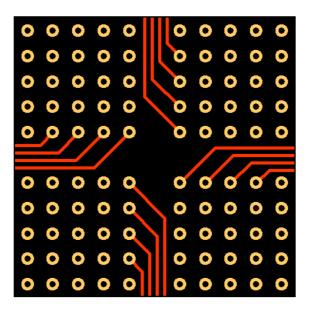

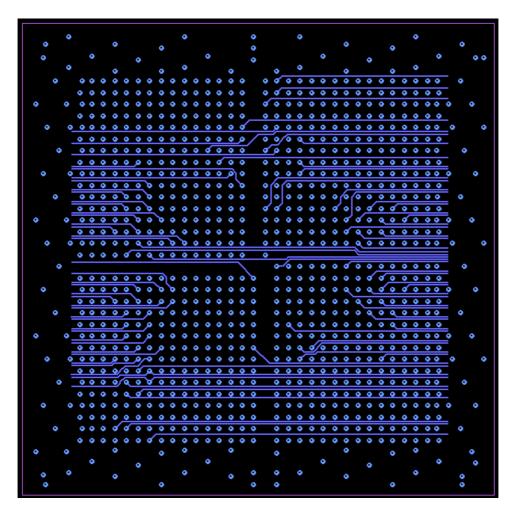

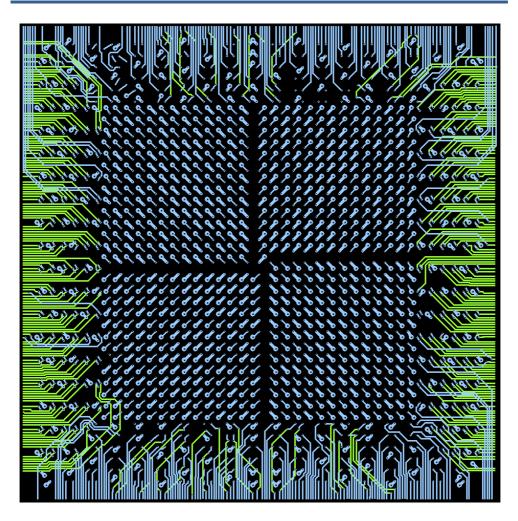

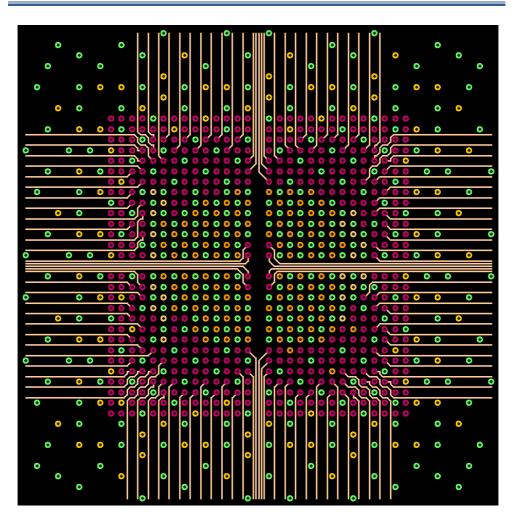

Figure 1-1: Breakout definition

Figure 1-2: Breakout example

#### **BGA Breakouts and Routing**

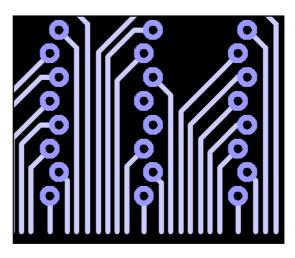

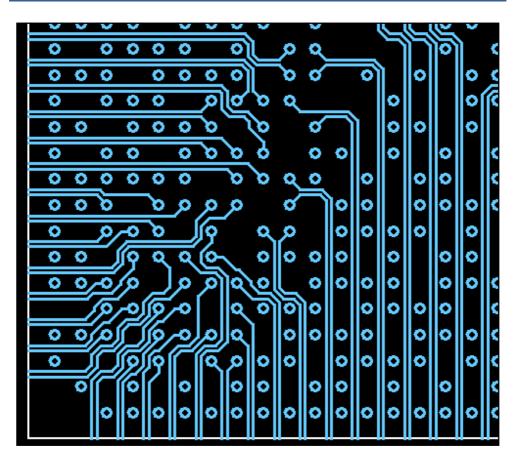

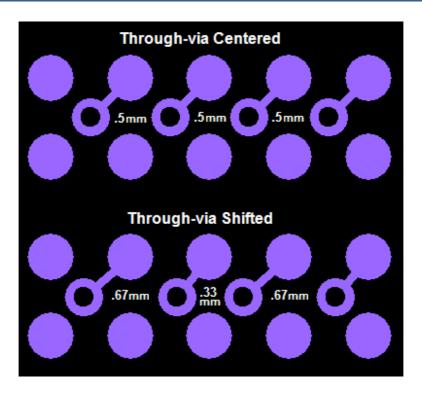

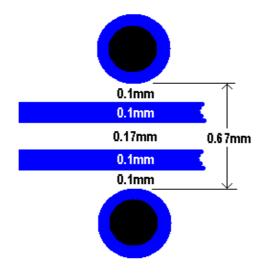

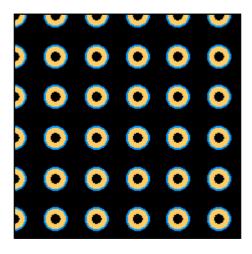

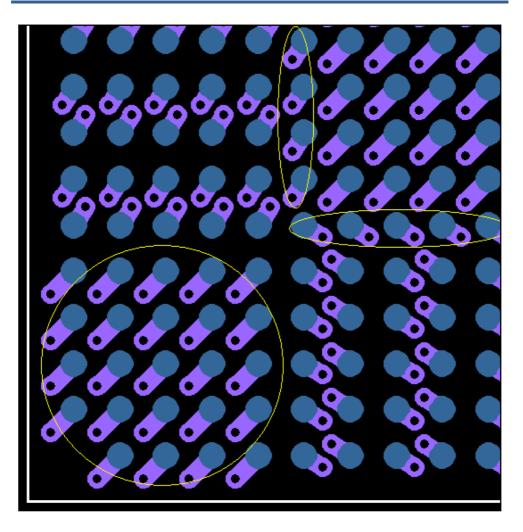

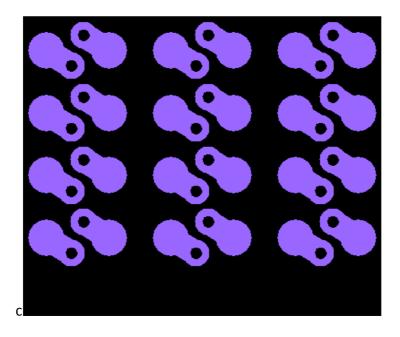

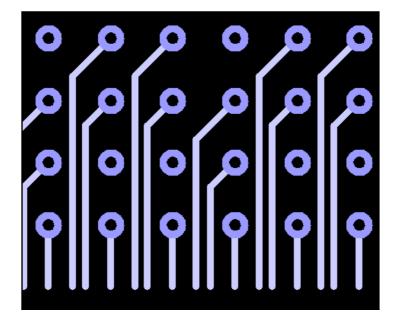

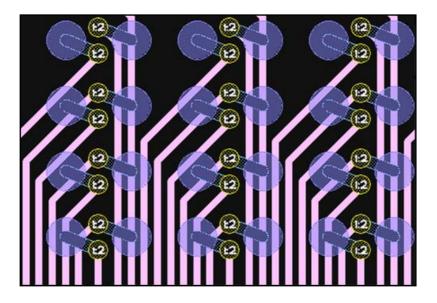

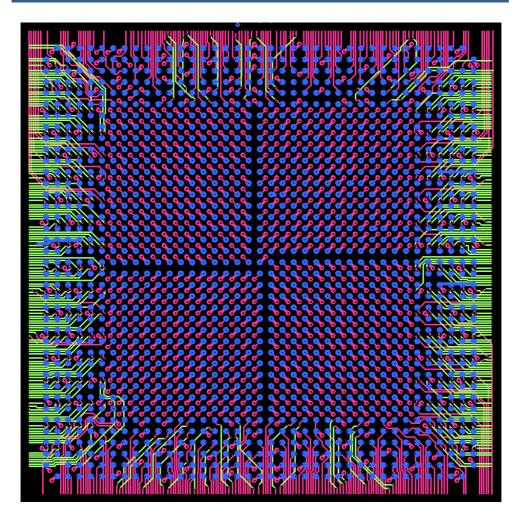

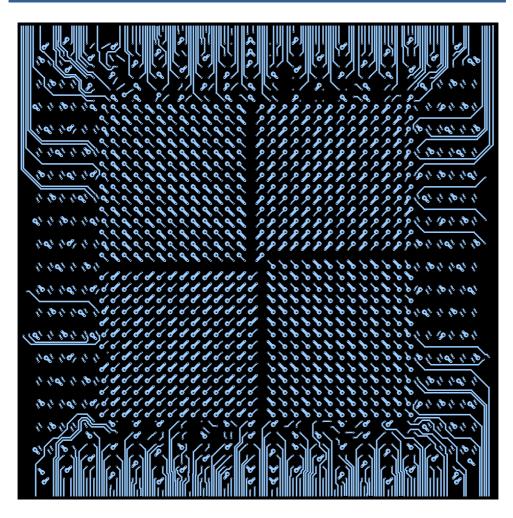

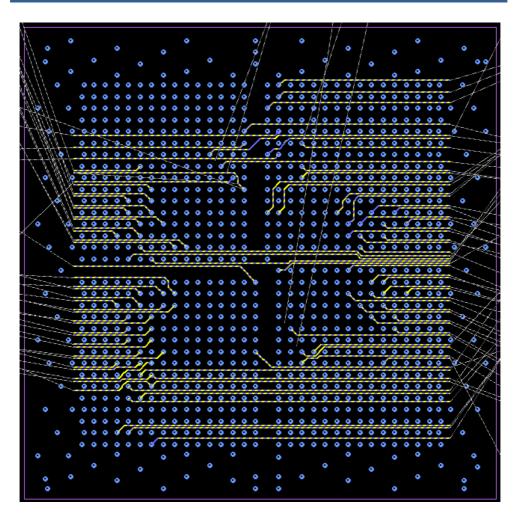

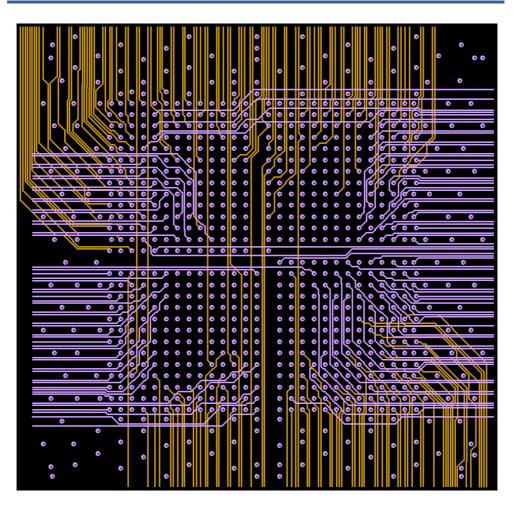

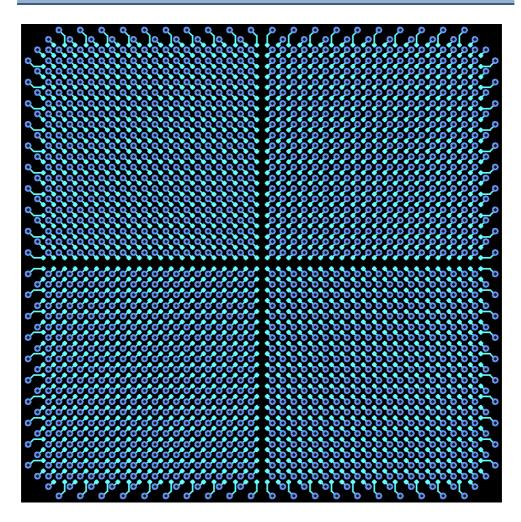

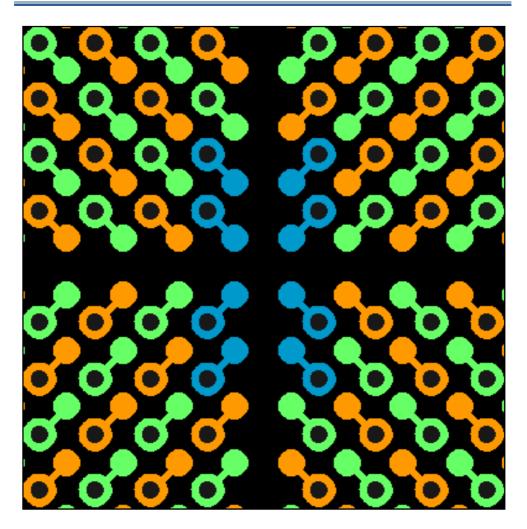

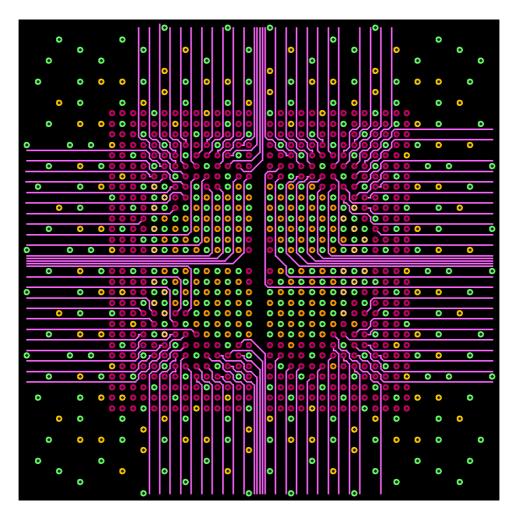

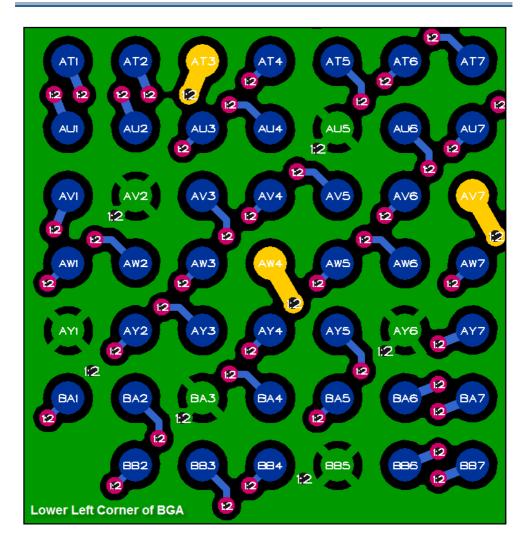

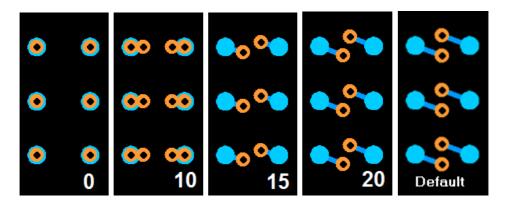

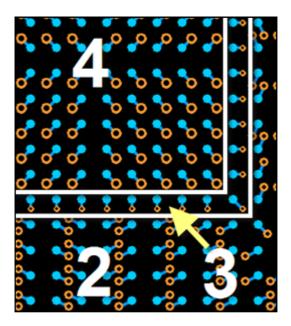

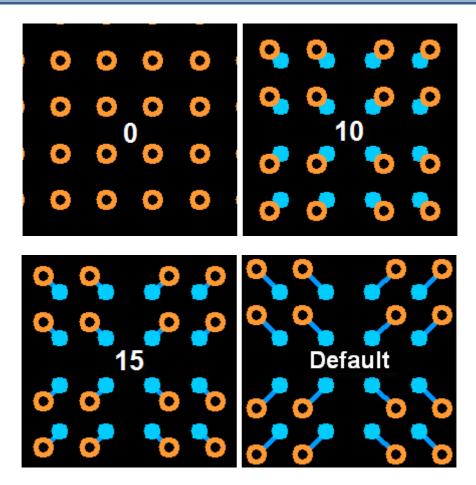

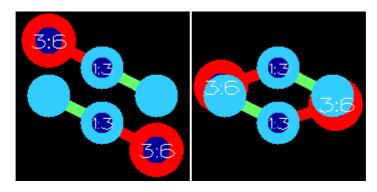

**Fanout Pattern** – When adding fanouts to the BGA, enabling routing on the inner layers, the pattern may vary considerably depending on the layer stackup, via model, and pin density. The pattern may range from simple quadrant-matrix to a set of complex alternating arrangements. Using the appropriate fanout pattern will make a significant difference on the success of breakout and routing of the BGA.

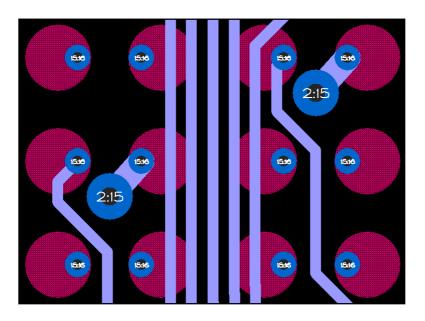

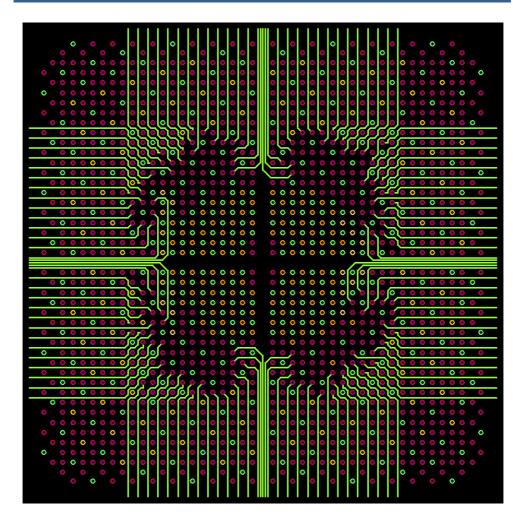

Figure 1-3: Simple matrix fanout pattern

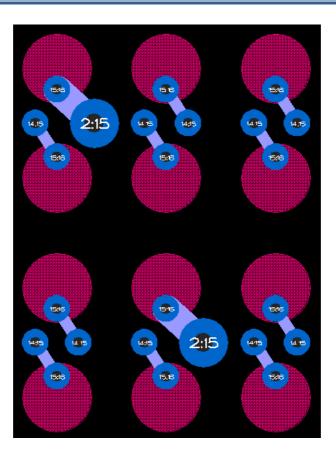

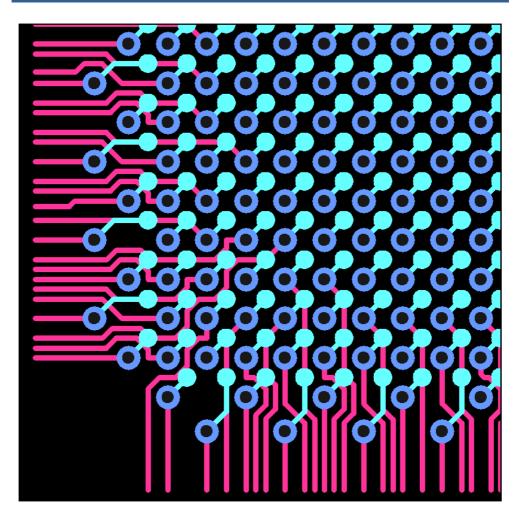

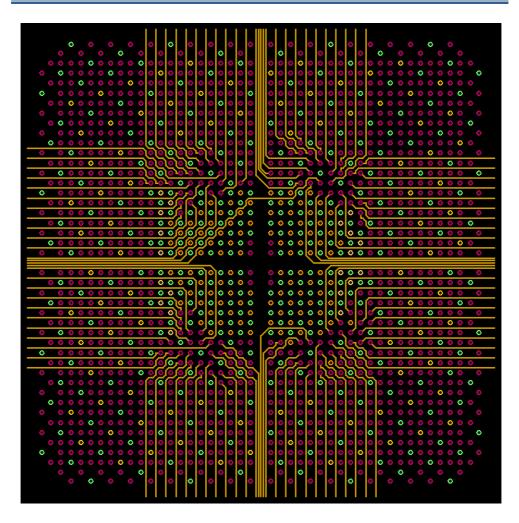

Figure 1-4: Shifted fanouts with more space for escape traces

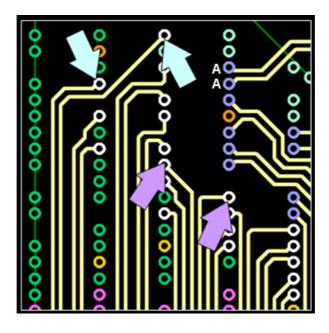

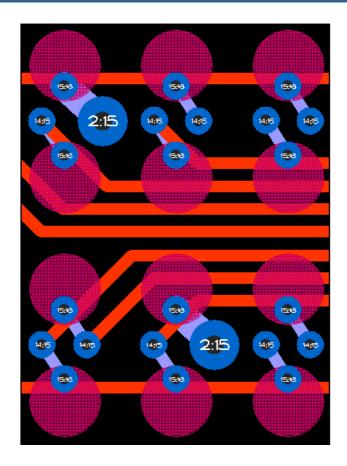

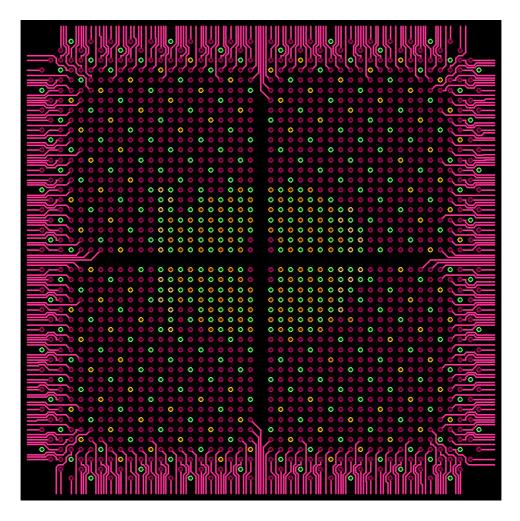

Figure 1-5: Multiple fanout patterns using blind, buried and through vias

#### Via Types

**Through-Via** – A via that extends from the top to the bottom of the board.

Through-vias are usually mechanically drilled and require an aspect ratio of 10/1 (length to hole diameter) for acceptable yields – often an aspect ratio of 8/1 is defined as the goal. It is usually larger than any other type of via, and as such, restricts routing space compared to smaller via types.

Blind-Via – A via that begins on an outer layer and ends on an inner layer.

Usually it will span 2-3 layers; however, there are no layer span restrictions except for those imposed by keeping the aspect ratio below 1/1 (length to hole diameter). The term is used to describe vias that extend from an outer layer to an inner layer in a sequentially laminated stackup (simply called blind-vias) and an HDI buildup stackup (called blind micro-vias).

Buried-Via – This type of via starts and ends on an inner layer.

The buried-via is used in combination with blind-vias in a sequentially laminated stackup, and micro-vias in an HDI buildup stackup.

**Micro-Via** – This via has a hole diameter less than or equal to 0.15mm (6<sup>th</sup>).

Generally it is laser drilled. Micro-vias may be a blind-via or buried-via and are used in HDI stackups.

**Any Layer-Via** – These are short micro-vias that individually span only a pair of layers and are stacked together to result in a span between any two layers.

#### **Stackup Types**

There many different stackups using different via spans, via types, layer counts, and materials. Most stackups in production fall into these categories: laminated with through-vias, laminated with blind and buried-

vias, and HDI buildup with micro-vias. The most common stackups are discussed in terms of route density, cost, signal integrity, and power integrity in Chapter 3, "Layer Stackups".

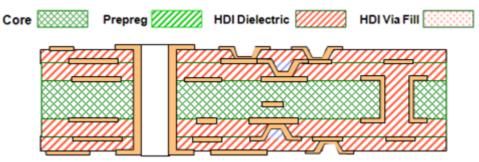

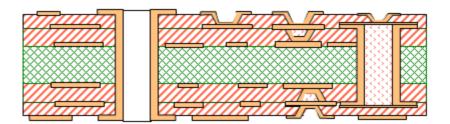

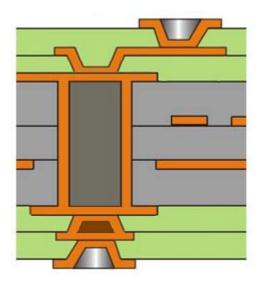

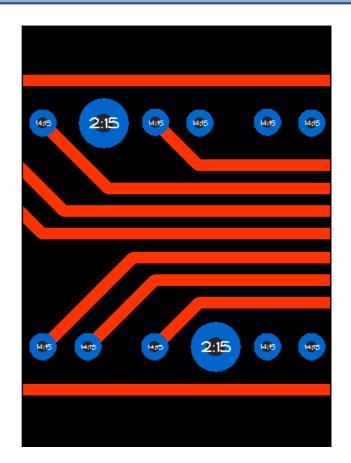

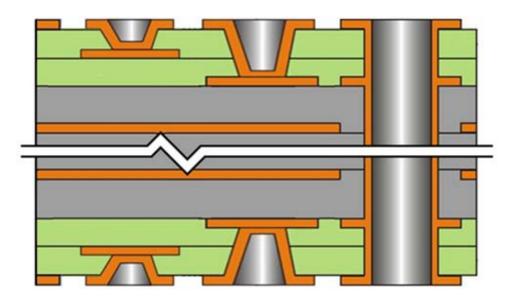

Figure 1-6: Laminated with through-vias

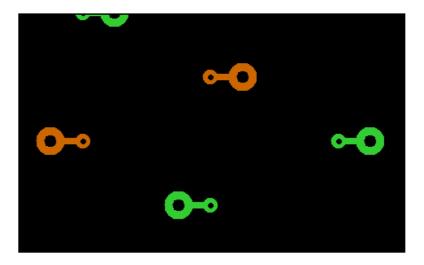

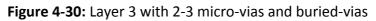

Figure 1-7: Laminated with blind and buried-vias Red = Blind-via, Orange = Buried-via

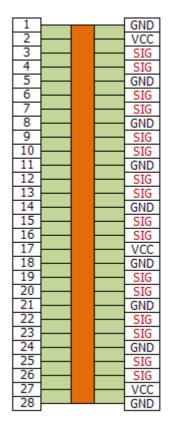

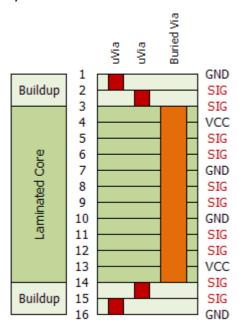

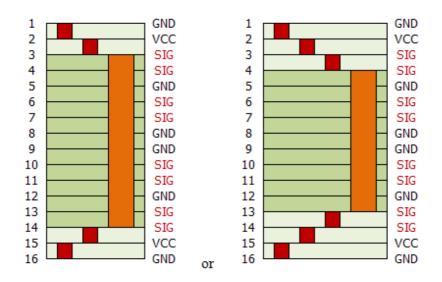

**HDI Buildup with Micro-Vias** – There are many variations of HDI of which here are a few:

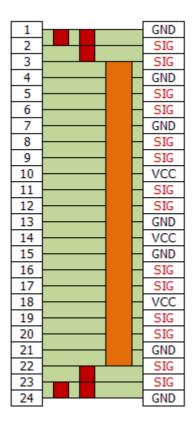

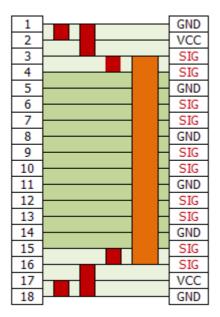

| 1  | L        | GND   | 1  | L         | GND |

|----|----------|-------|----|-----------|-----|

| 2  |          | VCC   | 2  |           | VCC |

|    | -        |       |    |           |     |

| 3  |          | SIG   | 3  |           | SIG |

| 4  |          | SIG   | 4  |           | SIG |

| 5  |          | - GND | 5  |           | GND |

| 6  |          | SIG   | 6  |           | SIG |

| 7  | ]        | SIG   | 7  |           | SIG |

| 8  | ]        | GND   | 8  |           | GND |

| 9  | ]        | SIG   | 9  |           | SIG |

| 10 | ]        | SIG   | 10 |           | SIG |

| 11 | <b> </b> | GND   | 11 |           | GND |

| 12 | ]        | SIG   | 12 |           | SIG |

| 13 | 1        | SIG   | 13 |           | SIG |

| 14 | 1        | GND   | 14 |           | GND |

| 15 | 1        | SIG   | 15 |           | SIG |

| 16 |          | SIG   | 16 |           | SIG |

| 17 | ╞╼┓╺┻    | VCC   | 17 | ╞╼┱╴┫╸╵╸╸ | VCC |

| 18 | ]        | GND   | 18 |           | GND |

**Figure 1-8:** HDI Variations Red = Micro-via, Orange = Buried-via

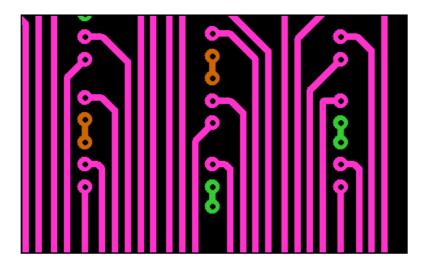

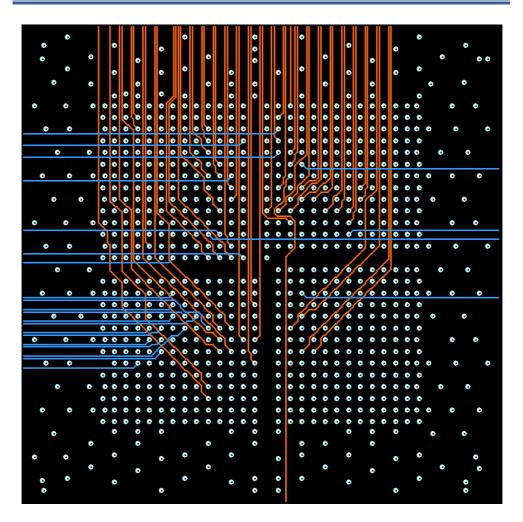

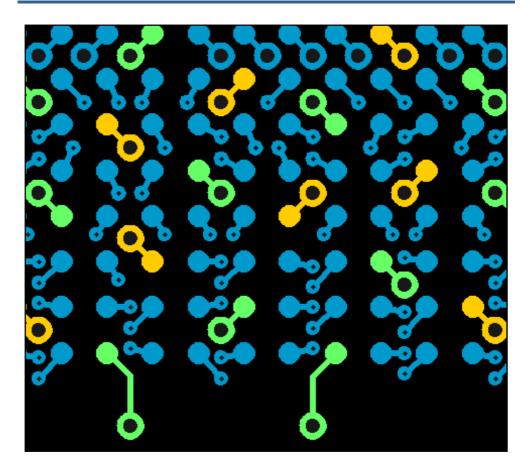

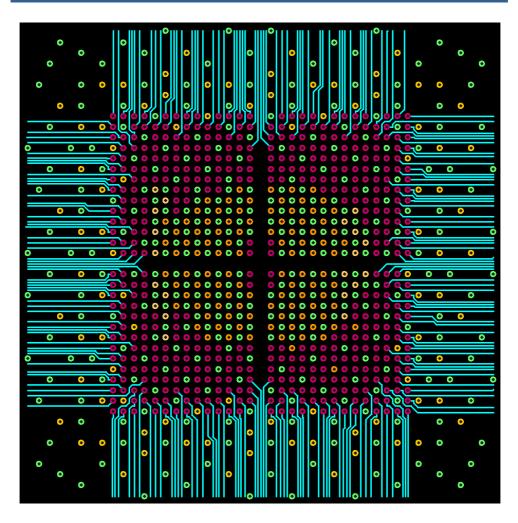

**NSEW Breakout** – North, South, East, and West routing of the escape traces. This means the escape traces are routed in all four directions on the same layer.

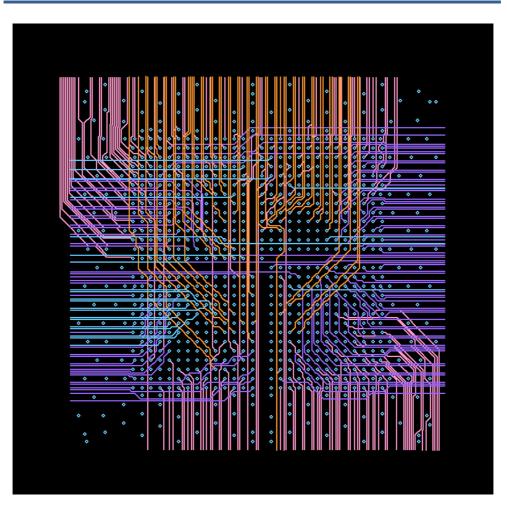

Figure 1-9: NSEW escape traces

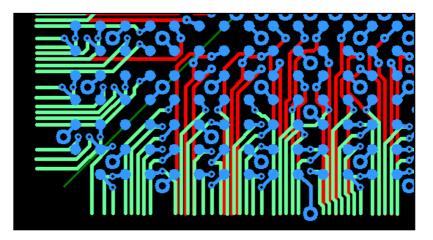

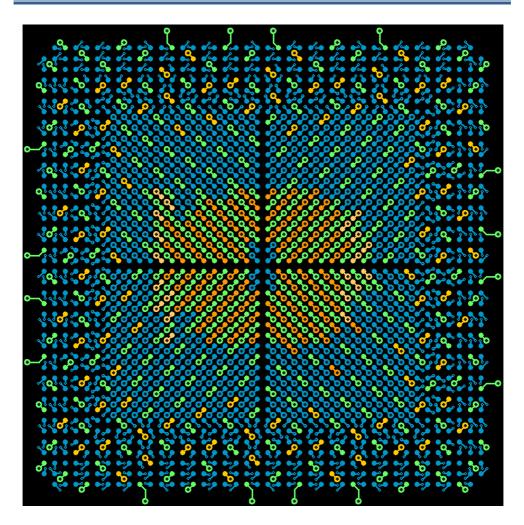

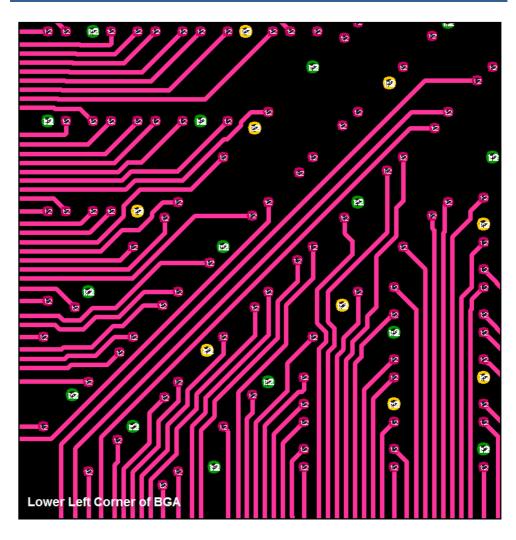

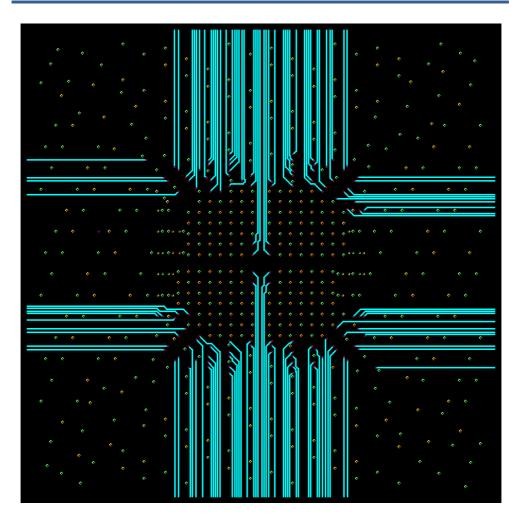

**Layer Biased Breakout** – The escape traces are routed in the direction of the layer bias as opposed to NSEW routing. Escape traces are also routed in the direction of the connection according to the layer bias.

Figure 1-10: Layer biased breakouts

Figure 1-11: Layer biased breakouts with escapes in direction of netlines

#### The Problem

The increasing pin-count and decreasing pin pitch of BGAs amplify already difficult design problems. Maintaining signal integrity at high performance levels and reducing fabrication costs are arguably the two most important requirements. Unfortunately, these requirements are conflicting. Reducing crosstalk is generally accomplished by increasing the space between conductors which can increase layer count, plus routing dense BGA packages require smaller design rules and more layers. Smaller features and increasing layers contribute significantly to board cost. This is nothing new; yet further miniaturization of BGA packages will make it even more difficult to maintain performance and cost goals.

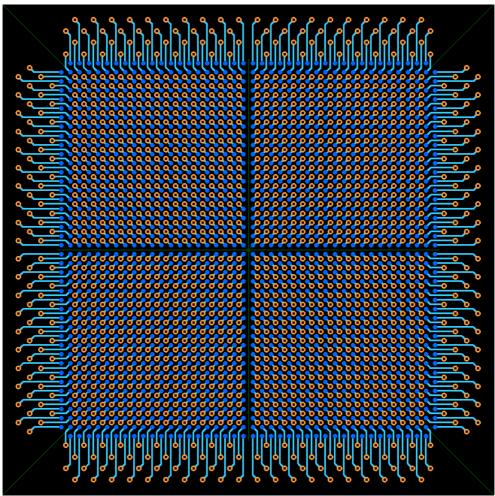

Many PCB designers who are designing with large pin-count BGAs (over 1500 pins) claim that the breakout of the device is the greatest contributor to increased number of PCB layers. An effective breakout solution will provide the foundation for layer reduction. I use the phrase "BGA breakout" to describe the method of applying a fanout solution and routing escape traces from those fanouts to the perimeter of the device prior to general routing of the PCB.

Why have breakouts? Why not just route the device without breakouts? The answer is simple. If the BGA device has too many pins in a dense array, the only way to minimize the number of layers is to utilize all the available space inside the component area with a pattern of fanouts and breakout traces. Routing such a device without an effective pattern will certainly waste space and require more layers.

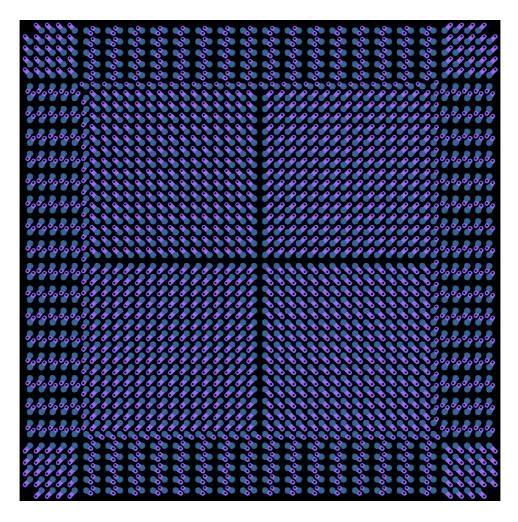

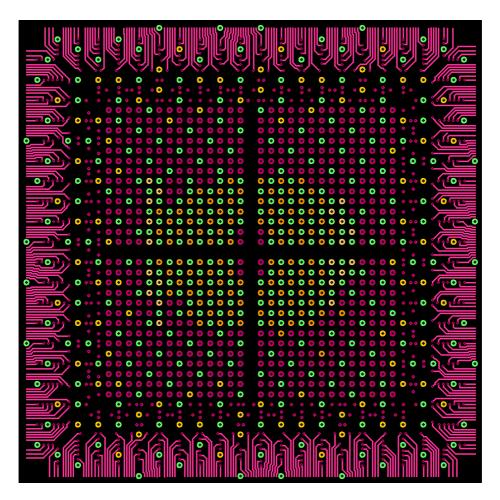

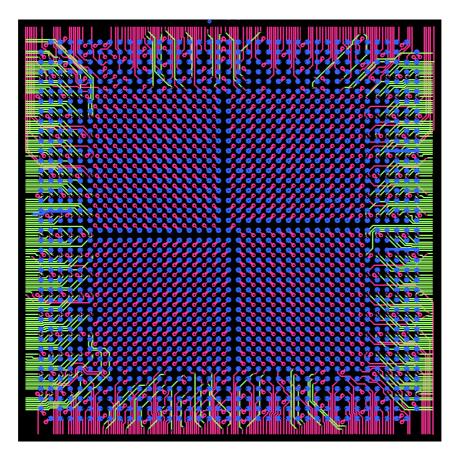

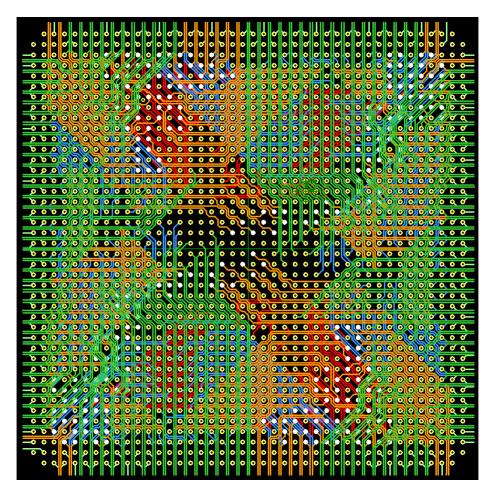

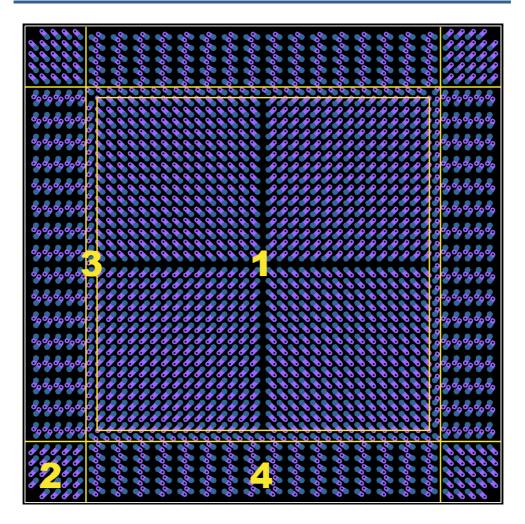

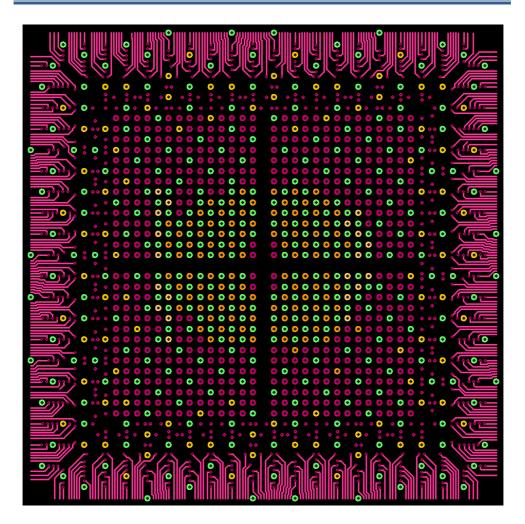

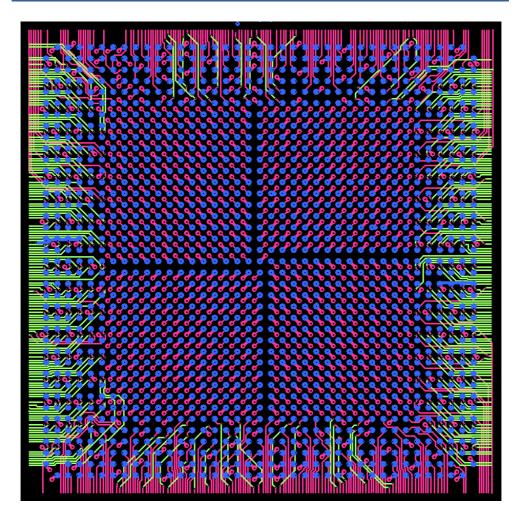

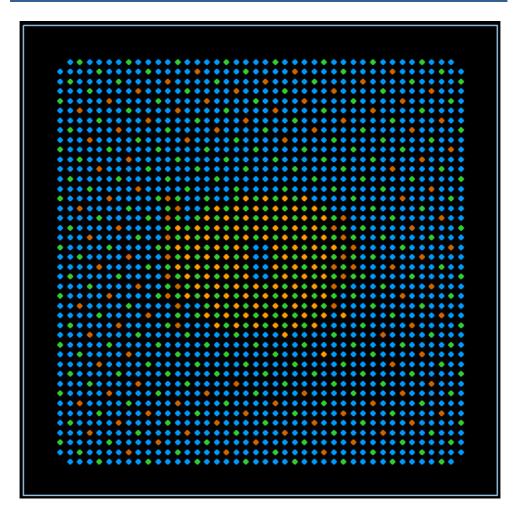

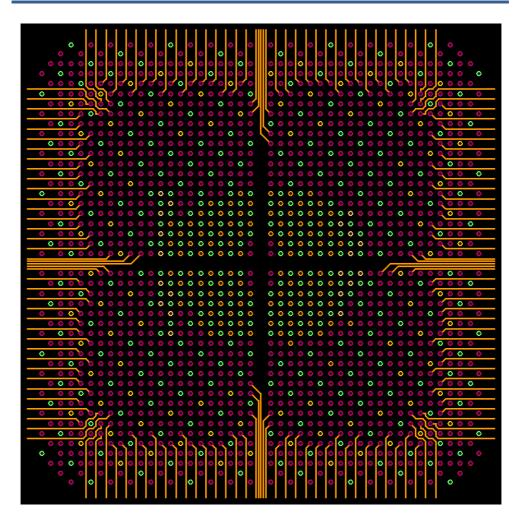

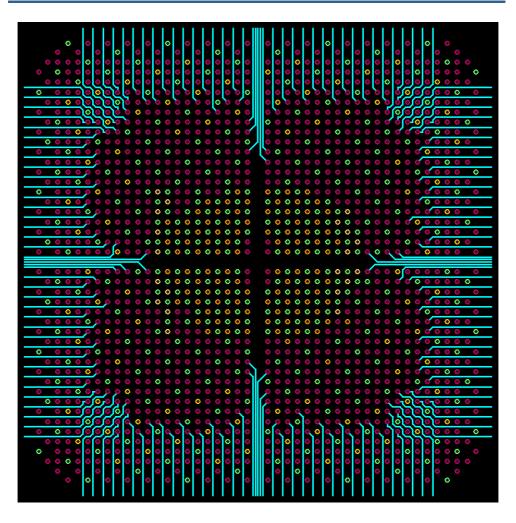

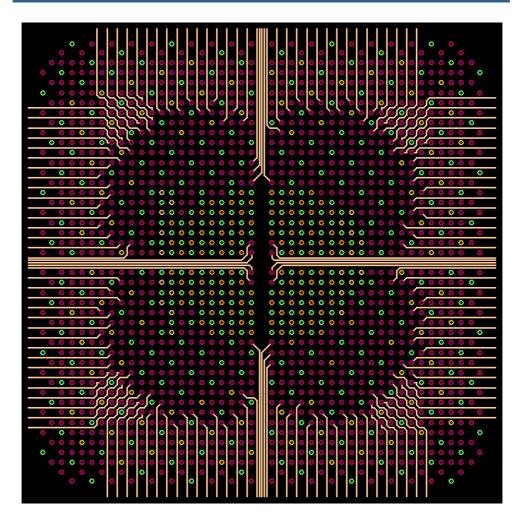

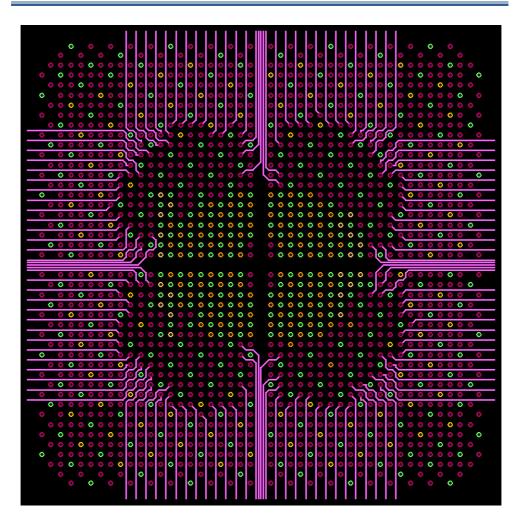

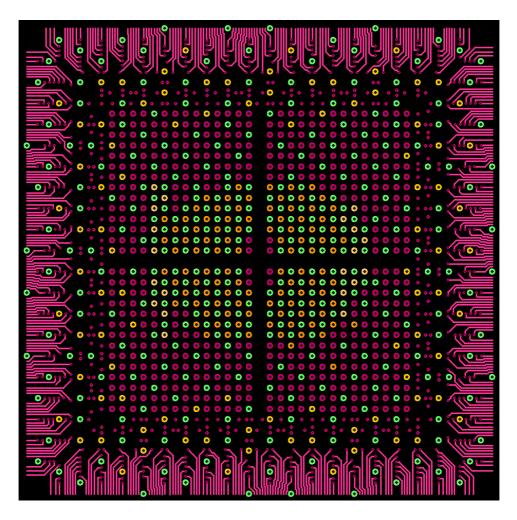

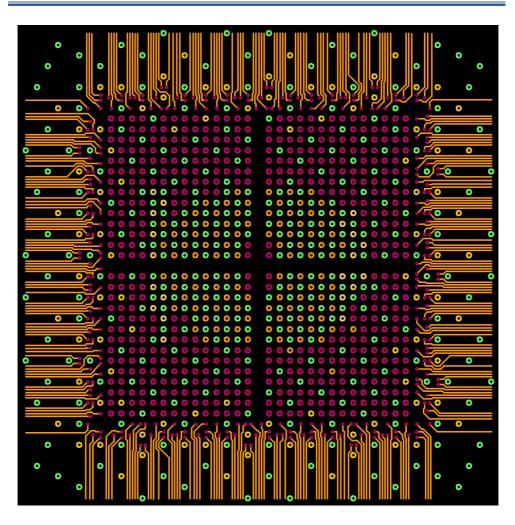

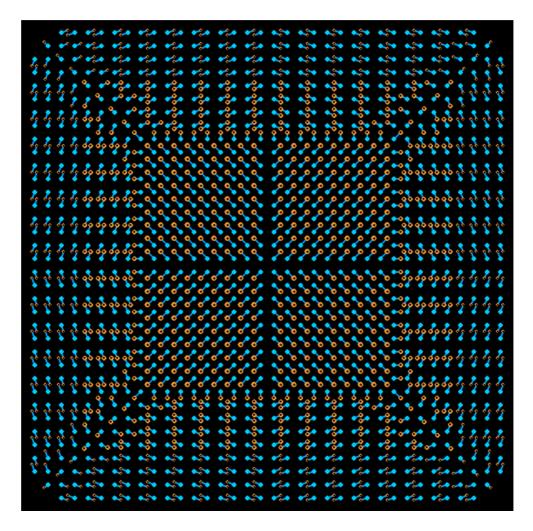

Figure 1-12: BGA breakout - 1760 Pins, 1mm pitch, fanout vias, and traces on multiple layers

Not all BGAs present a routing challenge. Low pin-count devices (less than 800 pins), even with a pin-pitch of less than 0.8 mm, do not present a significant breakout problem and are usually routed without a breakout method. This means the pins are generally accessible and can be routed with a reasonable number of layers. The high pin-count devices (over 1500 pins) with a pin-pitch of 1mm or less require a strategy for getting the traces out of the array. Without a breakout strategy, the layer count will be excessive thus affecting the fabrication cost and reliability of the PCB.

Additional factors complicate the breakout process. To attain the performance and cost goals, these items must be defined and managed properly and in concert with each other.

- Layer Stackup

- Via Models

- Design Rules

- Signal Integrity

- Power Integrity

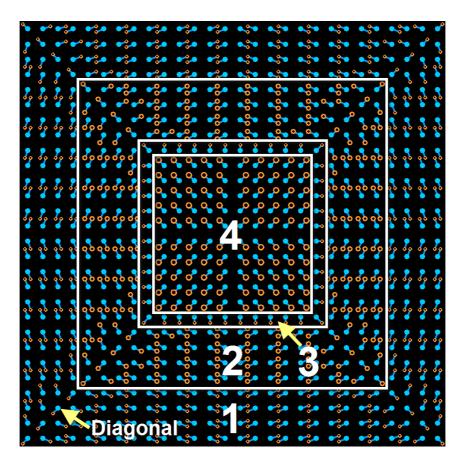

**Layer Stackup** - Early in the design process, the layer stackup will be defined. If the board has large and dense BGAs, High Density Interconnect (HDI) with a laminated core and buildup layers may be required. There are many different options using various materials and processes. Cost and reliability are usually the primary factors in determining the stackup and you will have to balance the tradeoff between layer count and fabrication processes to reach your goals.

**Via Models** - Within the context of any given layer stackup, you have many options regarding via models. The decision on which type of via to use (thru, laminated blind and buried or HDI micro vias) will likely be driven by the density of the board and the BGA packages. There are also options regarding vias inside pads and stacking that affect cost. In addition to this, board fabricators tend to focus on a limited set of processes thereby limiting your choice of vendors, depending on the technology you desire. From the design point of view, choosing the appropriate via models directly impacts the route-ability of the board.

**Design Rules** - PCB fabricators continue to find methods that allow for further miniaturization and increased reliability. The design rules have to balance the tradeoffs between cost, signal integrity, and route-ability.

**Signal Integrity** - Although the fabricators continue to improve their processes and produce reliable boards with smaller and features and clearances, maintaining signal integrity at high performance levels usually

requires greater spacing between critical nets, especially to manage crosstalk effects at higher speeds. This conflict is exasperated with high pincount and dense BGAs.

Choosing appropriate layer stackups and via models will not only improve route-ability but signal integrity as well.

**Power Integrity** - Managing power distribution effectively for large pincount BGAs is a challenge and is significantly impacted by the layer stackup. There are methods that can minimize the number decoupling capacitors required, thereby increasing the space available for signal routing.

#### **Solutions**

Because of the high number of variables with any PCB design, it is not possible to have a single BGA breakout solution for all situations. It is possible however, to develop solutions within reasonable sets of variables. This book offers principles for breakouts that may be applied as appropriate within the constraints of your own designs. It is my hope that in addition to finding useful ideas and methods herein, your imagination will be stirred to discover unique solutions.

# PRINTED CIRCUIT BOARD DESIGN

I/O Designer -- Uniting Disparate FPGA and PCB design flows

FPGA usage has become ubiquitous with applications spanning low power and low cost devices targeting consumer products to large 1500+ pin devices with multi-gigabit transceivers and embedded cores. Whatever the need, today's FPGA's can offer an attractive solution for a broad spectrum of applications.

But these new complex FPGA's require an effective FGPA / PCB co-design process to maximize their performance and benefit. I/O Designer provides support for over 1100 FPGA devices and superior PCB process integration. Automating manual tasks such as symbol and schematic generation can shorten design cycles by weeks. PCB quality is also improved by optimizing the FPGA I/O assignment based on the actual PCB layout with the push of a button. Optimized I/O assignments mean less route time, shorter traces and improved signal integrity.

To connect with other innovators and visionaries of future FPGA design join Mentor's PCB community at <u>http://communities.mentor.com,</u> call us at 800.547.3000 or for more information visit <u>www.mentor.com/products/pcb/system\_design/io\_designer</u>

## **Chapter Two - BGA Packages**

The good news is that BGA technology enables high pin-count FPGAs, ASICs, and connectors to be packaged with a very high density array of pins. The bad news is that finer pin pitches and increased pin counts are making these devices even more difficult to route. The requirement to miniaturize while increasing functionality is the most significant constant that drives change in our industry.

#### **High Pin Counts**

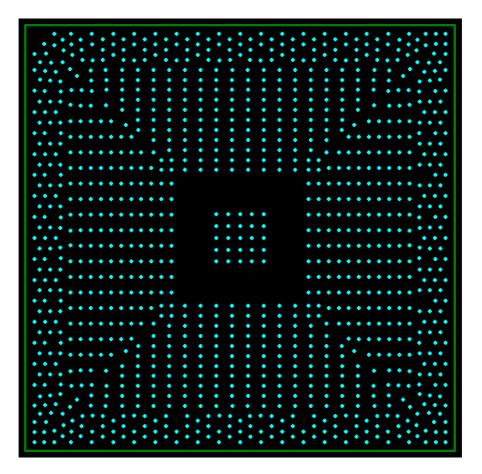

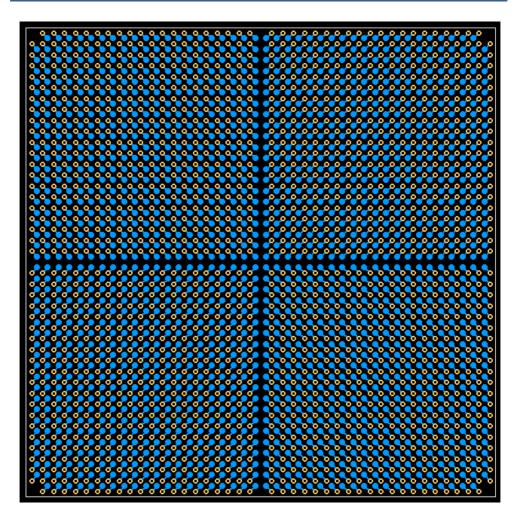

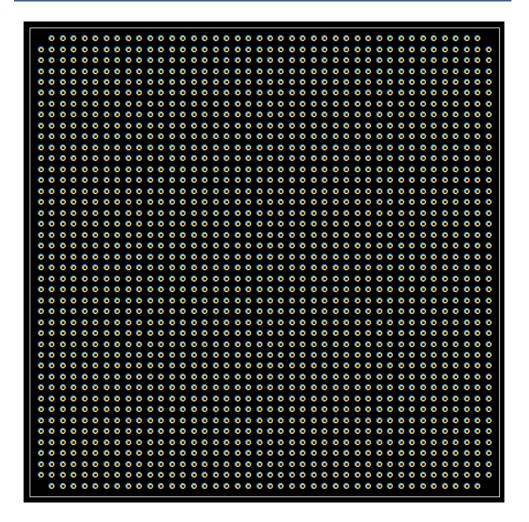

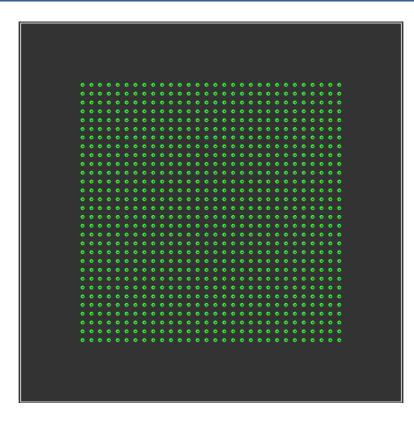

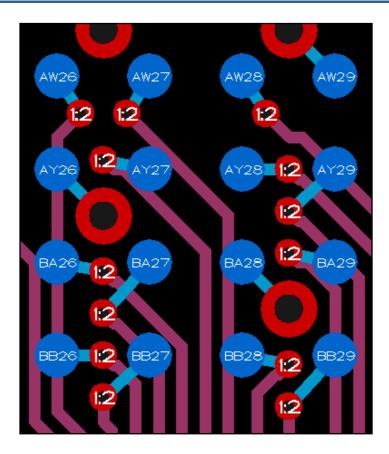

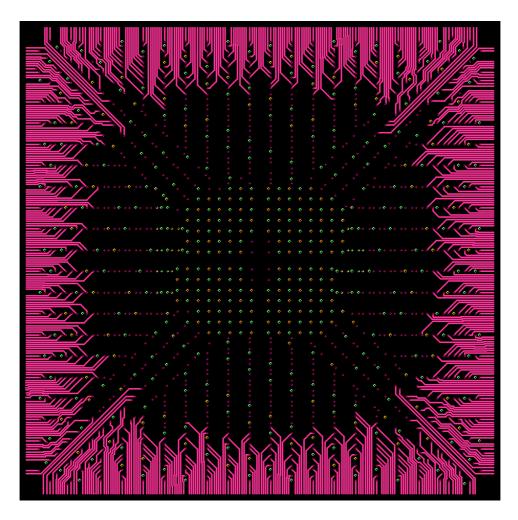

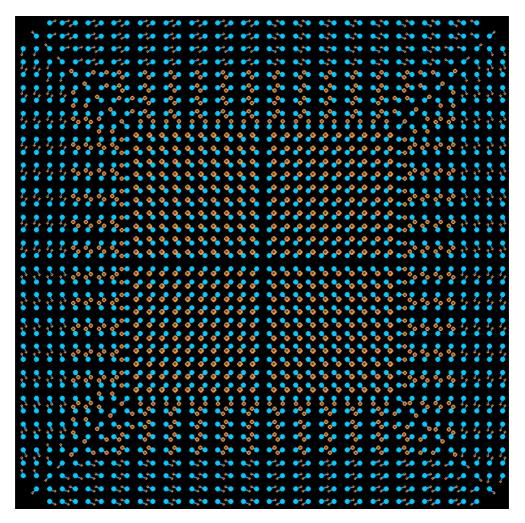

The current crop of BGAs with less than a 1mm pitch are not yet pushing high pin-counts and as such they can be routed fairly easily The very high pin-counts can be found in the 1mm pitch packages today and at 0.8mm in the coming years. Figure 2-1 shows a very high pin-count BGA.

In Table 2-1, the highest pin-counts for various FPGA and ASIC packages are listed.

#### BGA Breakouts and Routing

| Company      | Package      | Pins |

|--------------|--------------|------|

|              | .5mm Pitch   |      |

| Amkor        | fcCSP        | 180  |

| Actel        | CS281        | 281  |

|              | .8mm Pitch   |      |

| Quicklogic   | PT-280       | 280  |

| Altera       | DS-484UBGA05 | 484  |

|              | 1mm Pitch    |      |

| Actel        | FBGA 1152    | 1152 |

| Cypress Semi | 51-85179     | 1152 |

| eASIC        | 1152-FCBGA   | 1152 |

| Intel        | МСН          | 1300 |

| AMI Semi     | 1704 FFBGA   | 1704 |

| Lattice Semi | 1704 fcBGA   | 1704 |

| Xilinx       | FF1760       | 1760 |

| Altera       | DS-1760FBGA  | 1760 |

| NEC          | FCBGA 1849   | 1849 |

| Fujitsu      | FC_BGA       | 2116 |

| Toshiba      | PBGA[FC]     | 2304 |

| TI           | GTM (N2377)  | 2377 |

**Table 2-1:** High pin counts by manufacturer

Figure 2-1: TI GTM (N2377) BGA with 2377 pins at 1mm pitch

You can immediately see that a BGA with over 2000 pins presents a daunting routing task. Of course some large percentage of the pins will be power and ground; but even figuring out a good fanout pattern for those pins so they don't block routing is a challenge. Even if 40% of the pins are for power distribution, potential for 1400 signal connections still exists.

#### **Impact on Routing, Performance and Cost**

Since the pin-counts on 0.8mm pitch BGAs is still reasonably low, the routing task is not too difficult. However there are some consequences:

- Differential Pairs Unless the design rules in the device area are very small or innovative via patterns are used (to be described later in this book), the differential pairs must be split. Since these packages are still quite small, the split distance may not affect signal integrity.

- Potential Impedance Discontinuity If the pin-pitch is 0.8mm or less, often a rule area is used to allow smaller trace widths and spacing within the BGA area. The width change on single-ended nets will cause an impedance discontinuity as will a change in the spacing and or trace widths of a differential pair. The question that must be answered for each design is if this change across the rule area causes any significant ringing.

For the 1mm pitch BGAs, I consider a pin-count over 1500 to be one threshold for difficult routing. In the context of laminated FR-4 boards with through-vias, the following are some of the potential problems:

- Layer Count The sheer number of pins could require additional layers just to breakout the device. If you have multiple instances of BGAs over 1500 pins, then the route density will certainly force you to have more routing layers. Layer counts over 28 need thinner FR-4 dielectrics and de-lamination can occur at the lead-free assembly temperatures (at least 270° C).

- Via Aspect Ratio Maintaining high fabrication yields and long-term reliability requires the via length-to-hole diameter ratio to be less than 10:1, preferably 8:1. Boards with over 28 layers make it difficult to keep the through-via size small enough to allow effective routing. As the via pad size increases, it is more likely the differential pairs will have to be split during the breakout as well.

Nightmare of Circular Dependencies – High pin-counts dictate additional layers to route, additional layers require a larger via hole and pad size, and then larger vias reduce routing space, thus forcing additional layers. Once caught in this cycle, the best way to break out of it is to abandon through-vias and start using blind and buriedvias or HDI with applied dielectrics and micro-vias.

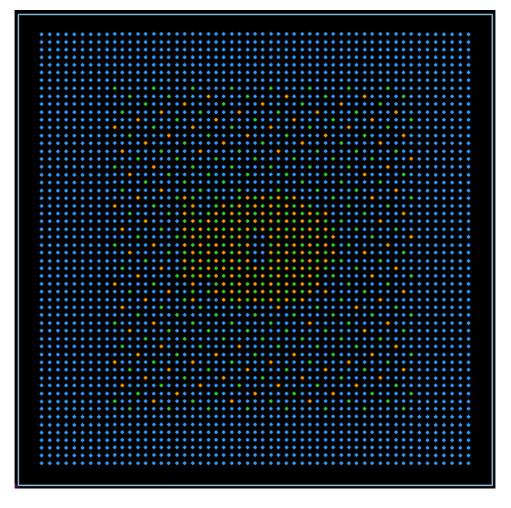

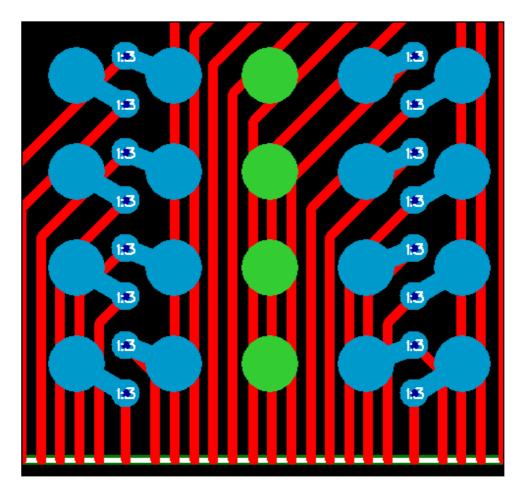

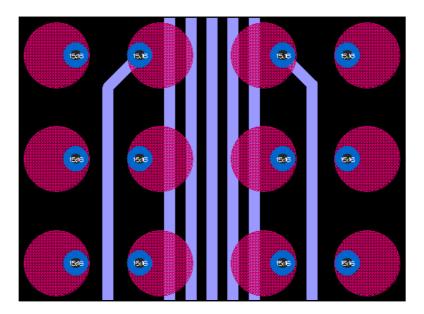

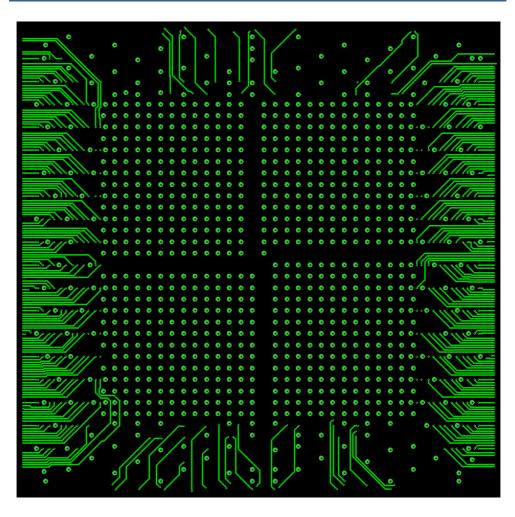

Greater than 2000 pins at 1mm pitch is a tipping point, especially if you have multiple instances of them on a single board as you might see in a network or emulation card. The layer count and via aspect ratio problems with laminated FR-4 boards will be even more severe with this many pins. When using blind and buried-vias or HDI micro-vias, effective fanout patterns can be used to increase route density from 24% to 36% with a corresponding layer reduction. Figure 2-2 shows increased route density on the first inner layer of a design when using blind-vias arranged in a pattern that allows for greater route density.

Figure 2-2: Effective fanout pattern

#### **Off-Matrix Ball Pads**

The Intel MCH (Memory Controller Hub) BGA package, which can have up to 1300 pins, is worthy of special mention. Figure 2-3 shows that the pins are positioned off the standard matrix making the routing difficult and depending on your design rules, it may require routing with any-angle traces. This is a newer package from Intel and gives us a view into the future — BGA routing isn't going to get easier anytime soon. Fortunately, PCB design software continues to be enhanced to keep pace with the evolving packaging methods.

Figure 2-3: Intel MCH package

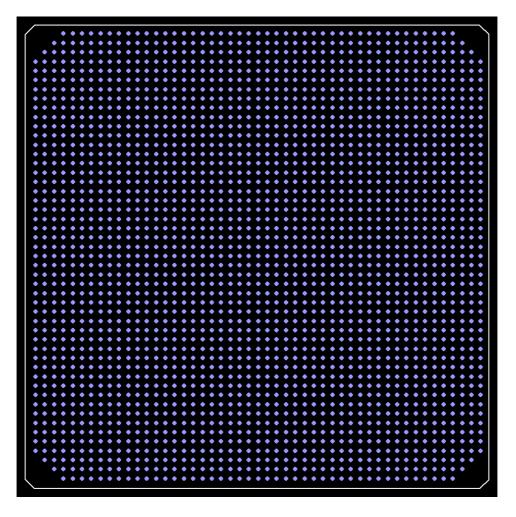

#### 0.8mm Pin-Pitch

The next figure not a real device, it just shows what could be done at 0.8mm pin-pitch in the same size package as the current 1mm pitch Virtex-5. It could contain 3025 pins.

Figure 2-4: 3025 pins at 0.8mm pitch (not real)

If you took the TI GTM (N2377) package and packed the pins in at 0.8mm instead of 1mm, it could have 3721 pins.

#### **The Near Future**

In order to increase functionality and continue to miniaturize, more pins will be added into smaller packages. I predict within the next 3 years we will see an ASIC or FPGA package at 0.8mm pitch and more than 2000 pins. This type of device presents more than a threshold; it is a tipping point because it will require the use of HDI. Managing signal integrity, maintaining fabrication yields and low cost will simply be impossible with the standard through-via laminate. Within 5 years, use of this kind of package will be common.

Design for Manufacture -- Design Anywhere, Build Anywhere

Accelerating development from concept to delivery is the key to profitability for today's electronic products. Fundamental to achieving this acceleration is effective information flow within and between organizations. Proper communication ensures that all stakeholders in the product delivery chain (PCB design, procurement, manufacturing, etc.) have their needs addressed.Collaboration, supported by Mentor's visECAD solution, enables the effective communication required to eliminate costly design defects and re-spins and maximize your company's profits.

To connect with other innovators and visionaries of future of manufacturing and collaboration, join Mentor's PCB community at <u>http://communities.mentor.com</u>, call us at 800.547.3000, or visit <u>www.mentor.com/pcb/manufacturing</u>

This page intentionally left blank.

## **Chapter Three - HDI Layer Stackups**

This chapter is intended to help designers who are creating large dense PCBs with multiple high pin-count BGAs and are finding standard laminate stackups inadequate to meet cost and performance goals. Maybe your laminate board has too many layers, or the feature sizes prevent effective breakout and routing of the BGAs. High Density Interconnect (HDI) stackups are a viable alternative and can provide lower cost with higher performance if designed properly.

From the information in this book, you should be able to determine which stackup methodology is best for your designs and why the alternatives may not be appropriate. If you just want to find out which stackups are recommended herein, you can just skip to the last section. However, to best understand the reasons why these stackups are recommended and the impact of choosing one of the alternatives, then it would be beneficial to read the whole chapter.

Defining the appropriate stackup should be considered as one of the most important aspects of initial design work. Since there are so many variables involved with stackups, this chapter will focus on stackups that enable effective board design with multiple large and dense BGAs. Typically this includes boards for the networking, computer, server and emulation marketplaces. It is assumed that even though handheld devices and consumer electronic products will likely have dense BGAs, it is unusual for them to have multiple instances exceeding 1500 pins and as such do not present the kind of design challenges being addressed in this book.

#### **Fabrication Vendors**

Stackups should be designed in conjunction with the fabrication vendor to minimize cost and meet signal integrity requirements. The board fabrication vendor ultimately builds a board that meets your requirements

#### BGA Breakouts and Routing

for cost, reliability, overall thickness, and impedance control. There may be additional requirements related to plating and specific materials. As a general rule, the vendor will adjust all the stackup variables as needed during their process to meet your goals.

The most productive method is to collaborate with the vendor on a stackup prior to designing the board. That way, the fabricator will be able to make minimal adjustments to meet your goals.

A good example of these adjustments is impedance control. Regardless of how carefully the stackup is defined with trace widths, material choices, dielectric and copper thicknesses, the fabrication process is not so exact. Each vendor has different equipment and methods. The lamination process shrinks the dielectrics and materials may be changed if not in stock or readily available. The tolerances in all areas add up and ultimately a reliable vendor has to make the right combination of adjustments in-process so that when measuring impedance on the test coupon, it fulfills your spec. Trace widths and material thicknesses may change a little but if the measured impedance is within spec then it really doesn't matter what changes were made – as long as the other requirements are not fatally compromised of course.

If the initial stackup is not defined properly, minor acceptable adjustments by the fabrication vendor will not be adequate to fulfill your overall requirements. A wise and experienced vendor will not accept the risk of making major changes to the design data.

#### Dependencies

Unfortunately there are many dependencies, some of them circular when defining a stackup. The process of determining an effective stackup can be overwhelming. Forgive the next meandering and confusing paragraph, but it is a good example of the difficult process of deciding which variables need to be compromised or emphasized to reach your goals: It is necessary to reduce the layer count to keep costs down. It is also required to have an adequate number of layers to route the board. On some of the largest PCBs, there are well over ten thousand nets to route. To control crosstalk, increase the spacing between traces which requires more layers. Also consider running the differential pairs together through the via array under the BGA, which means the via must be small enough to not only allow the diff pair to run together, but still space the traces far enough apart to attain the desired coupling. These traces also need to be the appropriate width in correlation to the thickness of the dielectrics and their material attributes to provide the desired impedance. But if you have too many layers, then the via needs to be bigger otherwise the aspect ratio of hole size to length becomes too great to drill with a good yield. If you make the via hole smaller, you can enable more dense routing but may sacrifice manufacturing yields. If you make the via hole larger, you may have to split the differential pairs through the via array and you will impact signal integrity and require more layers to breakout the BGA. If you have more layers, you will need an even larger via. These factors may require you to develop special fanout patterns in the context of the stackup to support the manufacturing, signal integrity and routing goals. This paragraph just touches a few of the dependencies; yet even so, it describes a daunting task.

Where do you begin? A number of example stackups will be presented with the advantages and disadvantages itemized along with a basic description of which via models, design rules work best. Some signal and power integrity concerns will also be discussed.

# **Overview of Stackup Types**

In the context of boards that have high pin-count BGAs, there are three stackup types of interest:

### 1. Standard Lamination with Through Vias

#### Advantages

- o Low cost (until layer count becomes too high)

- o Simple via models

- Simple dielectrics Primarily FR-4

- o Mature process, "everybody does it"

- High reliability (until layer count becomes too high)

#### Disadvantages

- o If layer count becomes too high

- Fewer fabrication vendors can obtain good yields, costs skyrocket

- Board can delaminate under high temperatures required for ROHS lead-free soldering

- Via has to be large, reducing route-ability, increasing layers

- o Difficult to implement for BGA pin-pitches below 1mm

- Through hole vias capacitively couple to every plane layer and signal losses increase with thickness

- Long via stubs create impedance mismatches, reflections on single-ended nets

- Large via pads often force differential pairs to be split under BGAs

#### Notes

- There are a number of tipping points where standard lamination with through vias is not viable

- Once the board is over 28 layers, it becomes difficult to manufacture with acceptable yields and therefore can become cost prohibitive.

- If the board is over 28 layers, the dielectrics can be so thin that de-lamination can occur under the higher temperatures required for lead-free soldering.

- Generally when using a few BGAs with less than 1500 pins and a 1mm pin-pitch, the breakout and routing of these devices is feasible using through vias.

- However, if you have a large number these on a single design, then the route density may force the layer count up high enough to limit the effectiveness of this stackup.

- If you have multiple BGAs with over 1500 pins and 0.8mm pin-pitch (or less) it is likely that through vias will make it very difficult to route these devices.

- When the thickness of the board due to the number of layers forces the via to be so large that it inhibits route-ability.

- Via length to hole diameter should be <10x otherwise reliability declines significantly

- o Pad diameter should be hole size plus 0.01 inch

- If the via pad is so large that it prevents differential pairs or multiple single-ended traces from being routed between the BGA via arrays, then more layers will be required to complete the routing.

- Vias can be shifted off the standard matrix under BGAs; however, with through vias, not much is gained.

#### 2. Sequential Lamination with Blind and Buried Vias

#### Advantages

- o Potentially shorter via stubs

- o Fairly simple via models

- o Generally smaller vias than required for through hole vias

- Minimum size for mechanically drilled vias are the same as for standard laminate; however blind and buried vias will likely have a smaller aspect ratio enabling more use of minimum via hole size, which is 8th.

- o Simple dielectrics Primarily FR-4

- Effective use of blind and buried vias opens up routing channels, potential for fewer layers

### Disadvantages

- Not a widely adopted process, more and more fabricators do HDI instead

- Minimum size for drilled vias is 8th

- Costs more than through hole laminated, yet minimum trace widths are still the same

- Practical reliability limits the number of sequential laminations to 2 or 3

#### Notes

- Sequentially laminated boards have the same tipping points as standard laminates; however, since the via length to hole size aspect ratio will be less and pad sizes can be smaller, route-ability improves and it is less likely that the design would exceed 28 layers.

- Since the feature sizes for traces can vias are still the same as with standard laminate, designing with multiple large BGAs of < 1mm is very difficult.</li>

### 3. Buildup with Micro-Vias (HDI)

#### Advantages

- Smaller feature sizes for vias and traces enables higher density and fewer layers

- Effective use of micro-vias opens up routing channels, potential for fewer layers

- Only practical way to design with multiple large BGAs having <0.8 mm pitch</li>

- Lowest cost for high density boards

- Improved signal and power integrity with appropriate stackup definition

- o Materials do well in processes requiring ROHS

- Newer materials available with higher performance and lower costs, which are not suitable for standard or sequential lamination

Disadvantages

- o Complex via models with many variations and still evolving

- Complex stackup definition

- Effective design methods on large dense designs have not been widely understood and documentation is sparse

- o Predictive design guides and cost estimates not yet available

Although HDI fabrication is pervasive in PAC Rim and China, North America slow to adopt

Notes

- HDI is the best alternative to high layer-count and expensive standard laminate or sequentially laminated boards.

- The trend is for higher pin-count and finer pin-pitch. The tipping point will occur when the >1500 pin BGAs use a .8mm pitch.

- The only way to effectively breakout and route multiple instances of these devices on a single board will be with the smaller HDI feature sizes.

- HDI currently dominates the fabrication technology for handheld and consumer electronics. For large board designs, it will continue to grow.

# **HDI Stackup Details**

This section is provided as a reference describing the relevant HDI stackup information based on the Institute of Printed Circuits (IPC) standard.

In this section Types I, II, and III are described. Type III is the recommended configuration for large dense boards with multiple high pin-count BGAs.

IPC information that may be useful to you:

http://www.ipc.org

**IPC/JPCA-2315** Design Guide for High Density Interconnects and Micro-vias

### IPC/JPCA-4104 Specification for High Density Interconnect (HDI) and Microvia Materials

### HDI Type I

This construction uses both micro-vias and through-vias in a structure consisting of a laminated core and a single micro-via layer on at least one side.

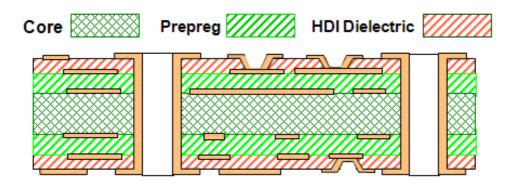

Figure 3-1: IPC HDI Type I

#### Notes

- The number of layers in the laminated core varies and is limited by two factors

- The through-via should have an aspect ratio (total length to hole diameter) less than 10x to maintain reasonable reliability.

- If the FR-4 dielectrics become too thin, they will delaminate under higher temperatures required for lead-free soldering.

Recommendations

- In the context of large dense boards with multiple high pin-count BGAs, this stackup will not be significantly better than laminate.

- The through via pads will need to be large.

- Using only a single micro-via layer will limit the ability to benefit from the smaller via and trace feature sizes.

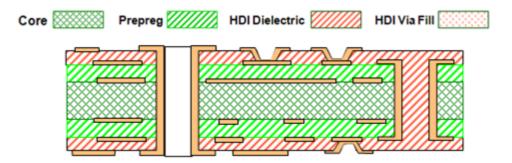

### HDI Type II

This construction uses micro-vias, buried-vias, and may have through-vias.

- There is a single micro-via layer on at least one side.

- Via holes are drilled in a laminated core and become buried when the dielectric material is added for the micro-vias.

- Micro-vias are staggered from other micro-vias and may be stacked or staggered relative to the buried vias.

Additional Notes

• See Type I note above on limiting the number of laminated core layers which applies to all variations of Type II through and buried vias.

Figure 3-2: IPC Type II

Figure 3-3: IPC Type II, variable-depth micro-vias

The variable-depth micro-vias can be in the form of skip-vias that connect only on the start and end layers.

Figure 3-4: IPC Type II, stacked vias

Recommendations

- In the context of large dense boards with multiple high pin-count BGAs, this stackup is better than Type I; however, is not adequate for the more difficult designs.

- Using buried vias instead of the through vias is a significant advantage.

- Using only a single micro-via layer span will limit the ability to benefit from the smaller via and trace feature sizes.

- The single micro-via layer span also restricts the viability of using the outer layers for a GND plane. Having only one buildup layer for routing traces isn't nearly as effective as two.

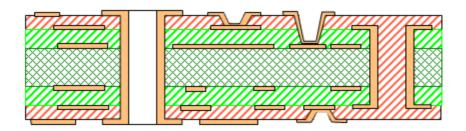

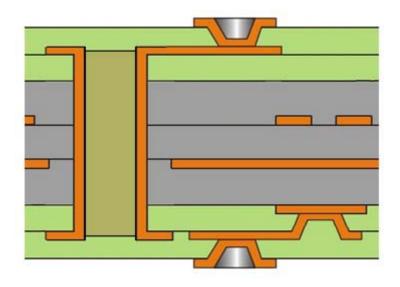

### HDI Type III

This construction uses micro-vias, buried vias, and may have through vias.

- There are at least two micro-via layers on at least one side of the board.

- Via holes are drilled in a laminated core and become buried when the dielectric material is added for the micro-vias.

- Micro-vias may be staggered or stacked with themselves and the buried vias.

Additional Notes

• See Type I note above on limiting the number of laminated core layers which applies to all variations of Type III through and buried vias.

Figure 3-5: IPC Type III

Figure 3-6: IPC Type III, stacked vias

Recommendations

- Type III HDI is the best stackup configuration for large dense boards with multiple high pin-count BGAs.

- With two micro-via layers there is considerable routing area available using the smaller via and trace feature sizes.

- Using the outer layers for a GND plane is feasible because there are still enough micro-via layers available for signal routing.

- Using stacked vias will allow for greater route density; however, the cost will be higher.

### HDI Type IV, V, VI

These additional HDI Types are defined in the IPC-2315 specification; however, they are not presented here simply because they are more expensive to fabricate and are probably not necessary for large dense PCBs with BGA breakout and routing challenges.

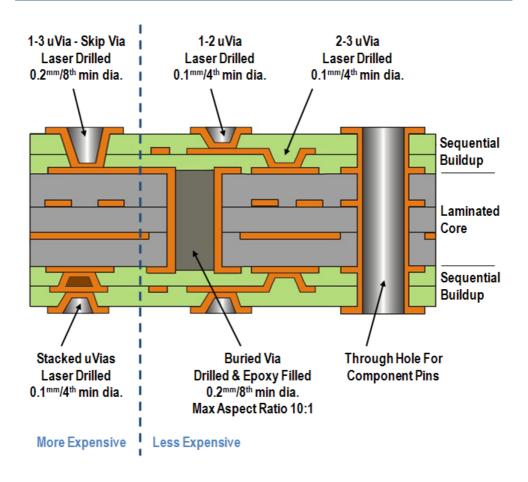

# Via Models

HDI Type III accommodates numerous via models and spans. Ultimately the via model that suits your design best will be driven by finding the least expensive method that will still enable adequate route density within the constraints of signal integrity.

The graphic below represents some of the via models that may be used in HDI Type III.

Figure 3-7: Type III via model examples

- Skip Vias This via model is effective for transitioning layers (because it emulates the stacked via); however it is not as efficient as stacked vias for route space due to the fact that the minimum diameter is 8th.

- Buried-vias As a general rule, all unused pads on the buried-vias should be removed. This will significantly reduce the crosstalk.

- Micro-via Pad Sizes Although the pad size will vary by fabricator, using a pad .15mm (6th) larger than the hole is adequate.

- Via Aspect Ratio Hole length to diameter: Micro-vias 5:1, buriedvias 10:1

### Alternative Via Spans

• Extending Buried-Vias

As shown below, you can extend the buried-via into the first microvia layer. This method can eliminate one drilling setup step.

Figure 3-8: Extended buried-via

Advantages

• If you have power and ground nets that need to extend all the way through the board, using the extended buried-via requires less space.

### Disadvantages

- Single-ended nets that use the extended blind via may suffer from additional via-stub effects; however, the additional stub length may be insignificant depending on the frequency.

- Depending on the fabricator, the cost of extending the buried-via may be slightly more than just having the buried-via in the laminated core.

• Stacking Micro-Vias and Buried-Vias As shown below, the micro-vias may be stacked with themselves and/or with the buried-vias.

Figure 3-9: Stacked vias

#### Advantages

- If you have power and ground nets that need to extend all the way through the board, using the extended buried-via uses the minimum space.

- Using stacked vias enables the most flexible and efficient via configuration for routing.

Disadvantages

• Stacking vias generally costs more due to additional steps required to ensure a good connection between the vias.

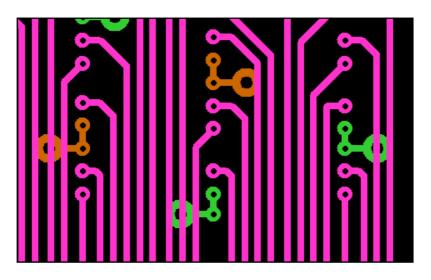

### **Plane Layer Assignments**

In the context of an HDI Type III stackup, location of the planes will impact your power distribution and integrity along with signal integrity. The appropriate location of planes is a much deeper and more complicated subject than can be addressed in this book; however, certain methodologies are recognized as effective and will be described at a high level herein.

In the stackups shown, the number of layers in the laminated core is variable of course. Sixteen layers is just convenient for the purpose of showing plane layer assignments graphically.

Outer Layer GND

A stackup such as the one pictured is typical when GND is assigned to the outer layers.

Figure 3-10: Outer layer GND

Advantages

- GND on the outer layers provide an excellent EMI shield.

- If the bypass capacitors for the BGA are placed on the same layer as the BGA, then you may minimize the number of vias

used for GND underneath the BGA. This will open routing channels which may be critical for an extremely dense board

• You may still want vias for some of the GND pins to improve the return paths

Disadvantages

- If the return paths are managed with a minimum number of GND vias, there really isn't a downside to using this method.

- It is often thought that using the outer layers for GND will limit the number of buildup (smaller features) layers for routing signals. Although this is true, it is also important to consider that controlling the signal integrity of those nets will be more difficult and burying the first GND plane in the laminate structure will result in the routing on the micro-via layers to not have a good reference plane.

#### • Outer Layer GND and VCC

A stackup such as this one is typical when GND is assigned to the outer layers.

Figure 3-11: GND and VCC on outer layers

### Advantages

This scheme has the same advantages as listed for "Outer Layer GND" plus these additional ones:

- The capacitive coupling between the GND and VCC layers will be excellent minimizing the bypass capacitors needed for the BGA (assuming you use a relatively thin dielectric less than .05<sup>mm</sup> or 2<sup>th</sup>).

- This is also an opportunity to use embedded capacitors and pull-up resistors effectively; resulting in opening up considerable routing space on the signal layers.

#### Disadvantages

If the return paths are managed with a minimum number of GND vias, then there really isn't a downside to using this method.

Recommendations

- Using a skip-via or stacked-vias would be good for this kind of stackup if it can be cost justified.

- Split Planes

Often large BGAs require multiple voltage supplies. You can use split planes or dedicated voltage layers for this power distribution. If this method is used, it is best to add a couple voltage supply layers in the center of the board surrounded by GND planes to avoid having signal layers affected by crossing the splits or different voltages.

# Layer Count

The number of buildup and core layers required to route the board and fulfill the performance and signal integrity requirements will vary depending on the route density and manner in which you decide to manage the plane layer assignments. Determining the route density is a subject outside the scope of this book; however, as a general rule for large dense boards start with 8-10 signal layers and increase them as needed during the routing process.

Since the thickness of the laminated core will be limited by the aspect ratio of the buried via (10:1), work with your board fabricator to determine core and prepreg thicknesses. Doing this in conjunction with trying to minimize via pad size for routing will enable you to determine the high-end number of layers available in the laminated core.

# **Design Rules**

Throughout this book, the minimum values for via hole and pad diameter as well as the aspect ratios have been described. These minimums are used as a guide to enable high yields. Minimum trace widths and clearances are based upon the fabricator's capabilities; however, they are more than likely to be set based on signal integrity requirements such as impedance control and minimizing crosstalk.

### **Fanout Patterns**

The method used for fanout of BGAs is a subject of an entire chapter and can significantly contribute to the success or failure of the design. Here are some of the considerations:

- Via location relative to BGA pad

- Adjacent (dog-bone)

- o Partial via-in-pad

- o Offset via-in-pad

- o Via-in-pad

- When using a combination of micro-vias and buried-vias, each via span can have its own pattern within the BGA and as such can affect the route-ability of the device.

- Via-in-pad methods provide the greatest opportunity to increase route density.

- Shifting and aligning the vias may be useful to improve route-ability.

- Using a complimentary patterns for the micro-vias and buried-vias can improve route-ability

- The goal should be to reduce the overall "effective" number of pins by the time you get to the laminated core, thus reducing the number of layers required to breakout and route the BGA.

# **Signal Integrity**

This is a subject that has many dependencies, variables and thousands of articles. The desire here is to simply point out a few design methods related to large board HDI stackups that could positively affect signal integrity:

- Remove unused pads on buried vias to reduce crosstalk.

- Route the high-speed single-ended nets on the buildup layers closest to the component. The potential for via stub effects is eliminated because buried-vias are not used.

- Route differential pairs on the laminated core layers. The via stubs affect the differential pairs less than the single-ended nets and the crosstalk between the diff pair vias (if the unused pads are removed) is likely to be insignificant.

- A stripline configuration, where pairs of signal layers are sandwiched between plane layers, not only provides the best return paths but also reduce crosstalk. This supports the notion that using a ground plane on the outer layers is a good practice.

# **Recommended HDI Stackups**

What are the best HDI stackups for BGA breakouts and routing? It depends on your priorities. The following stackups were analyzed for relative cost, route density, power integrity and signal integrity. The three are rated at the top with the priority given to route density with good power and signal integrity.

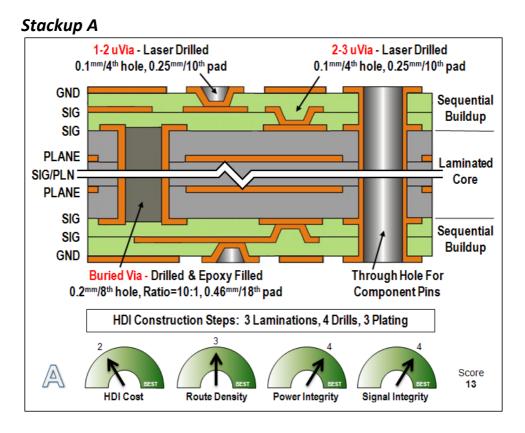

Figure 3-12: Stackup A

Stackup A Comments:

- Total score = 13

- This is a great average of the variables and a good stackup if you are starting out with HDI.

- The via models are simple and it won't be difficult to find vendors who can fabricate them.

- The ground plane on the outer layers provides a high rating for power and signal integrity.

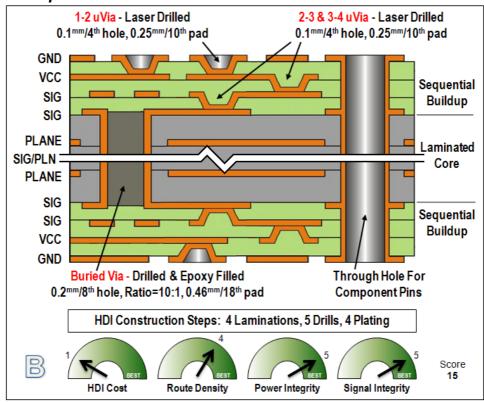

### Stackup B

Figure 3-13: Stackup B

Stackup B Comments:

- Total score = 15

- The GND and VCC on the outer layers provide the best power and signal integrity.

- The additional buildup layer increases the cost (more laminations, drills, and plating steps) but also improves the route density as opposed to losing an HDI routing layer due to the VCC plane.

- The via models are simple and it won't be difficult to find vendors who can fabricate them.

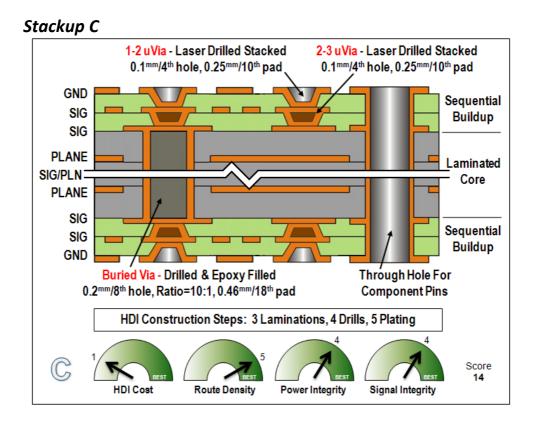

Figure 3-14: Stackup C

Stackup C Comments:

- Total score = 14

- The stacked vias enable the best route density but also increases the cost and may limit the number of vendors who can fabricate this stackup.

- The ground plane on the outer layers provides the high rating for power and signal integrity.

# **Secondary HDI Stackups**

These stackups are useful in their own way depending on your priorities; but they not as good overall as the Top 3.

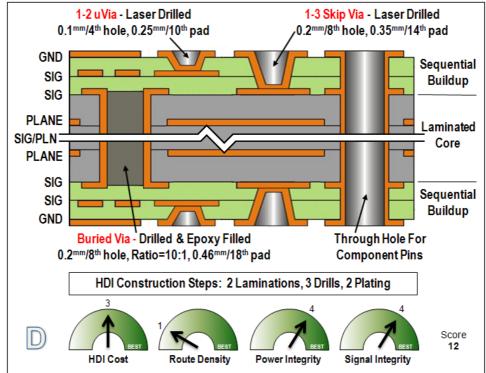

### Stackup D

Figure 3-15: Stackup D

Stackup D Comments:

- Total score = 12

- The ground plane on the outer layers provides the high rating for power and signal integrity.

- The skip via reduces laminations and plating steps, which lowers cost; however, contributes to a relatively low route density.

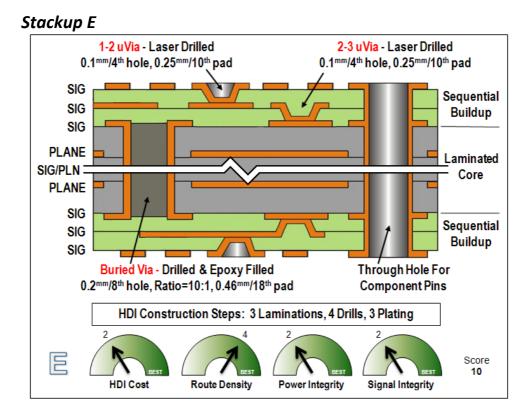

Stackup E Comments:

- Total score = 10

- The lack of a ground plane on the outer layers reduces power and signal integrity; however it does provide for improved route density assuming routing would be done on the outer layers.

- The via models are simple and it won't be difficult to find vendors who can fabricate them.

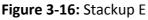

### Stackup F

Figure 3-17: Stackup F

Stackup F Comments:

- Total score = 14

- The ground plane on the outer layers provides the high rating for power and signal integrity.

- The extended buried via reduces the lamination and plating steps which lowers cost; however it reduces route density.

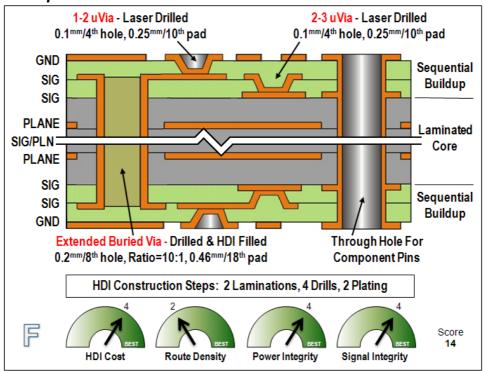

Figure 3-18: Stackup G

Stackup G Comments:

- Total score =14

- The ground plane on the outer layers provides the high rating for power and signal integrity.

- The extended buried via and the skip via reduces the lamination and plating steps which lowers cost; however it also reduces route density.

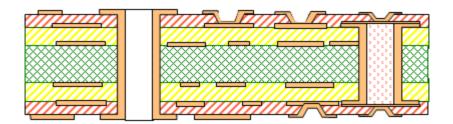

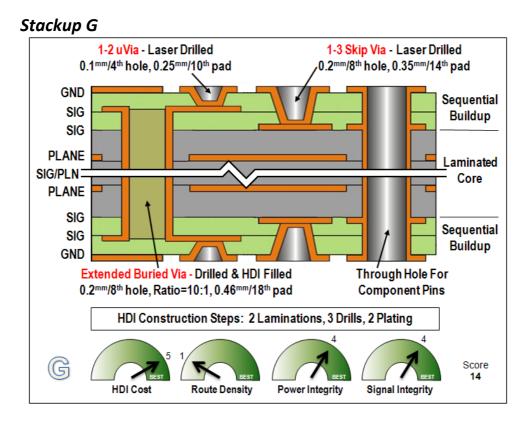

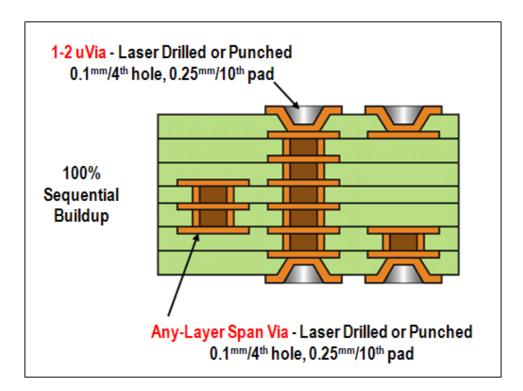

# Any-Layer-Via Stackups

The any-layer-via stackup is an HDI variation that although currently expensive will become affordable over time and in my opinion provide the kind of stackup and via models that will be required for successful routing of very large and very fine-pitch BGAs. As you can see in Figure 3-19, vias can span any set of layers.

Figure 3-19: Any-layer-via stackup

The micro-vias are either punched or laser-drilled and are filled with a conductive material after each buildup stage in the metallization process to connect them. Although Matsushita Corporation originated the ALIVH (Any

Layer Interstitial Via Holes) numerous other companies are developing new processes that allow for micro-vias to span any layers.

Chapter 6, "0.8mm Pitch BGA Tests", applies the any-layer-via method and demonstrates the great advantages of this via model.

### Summary

There are many variations available for HDI stackups. The one you choose to use will have to balance the cost, route density, signal and power, and integrity. New fabrication methodologies continue to evolve and within a few years you will have even more possibilities.

Happy Holden, PCB Technologist at Mentor Graphics, has written scores of articles and presentations on HDI. His body of work may be found at www.mentor.com/pcb and www.westwoodpcb.com. His expertise and knowledge is described in tremendous depth and will certainly provide great insight to HDI materials, best practices and the impact on signal and power integrity.

# PRINTED CIRCUIT BOARD DESIGN

The secret to successful high speed PCB design

Simulate fast driver edges and new bus technologies with HyperLynx<sup>®</sup>, the most widely used high-speed PCB simulation software. HyperLynx provides both pre- and post-layout analysis of signal integrity, flight times, cross-talk, and multi-gigabit SERDES technologies and is compatible with all major PCB design flows.

To connect with other innovators and visionaries of future high-speed design join Mentor's PCB community at <u>http://communities.mentor.com,</u> call us at 800.547.3000 or for more information visit <u>www.mentor.com/products/pcb/analysis\_verification</u>

# **Chapter Four - Fanout Patterns**

The effectiveness of a fanout pattern on large BGAs contributes significantly to the route-ability of a design which impacts the layer count, which in turn affects the cost of the board fabrication. The fanout of a BGA is only a part of the routing solution, which also may include escape traces along with the general interconnect routing of the pins.

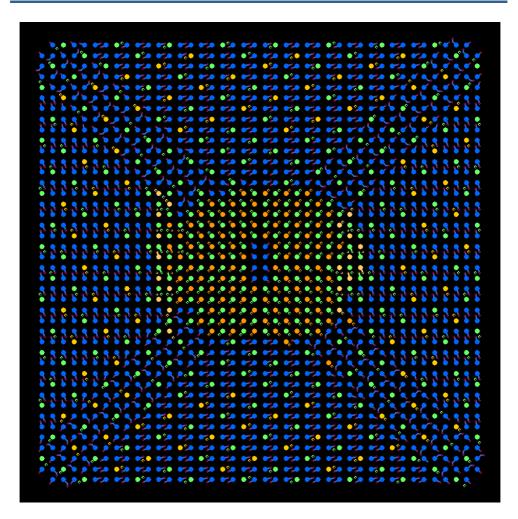

Since there are many variables involved in determining fanout patterns, such as layer stackup, via models, via spans, and design rules, this chapter will explore fanout patterns BGAs in the context of large, dense boards where minimizing layer count is important.

The goal of the BGA fanout effort should be to eliminate the BGA routing as the primary contributor to the number of layers while maintaining signal integrity and fabrication yield requirements. This chapter offers numerous ideas and methods that may or may not be useful in the context of your design requirements. Hopefully you will find some of them useful to reduce layer count, increase route density and meet your performance goals.

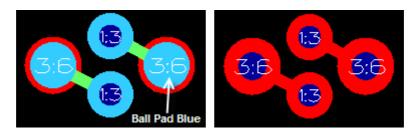

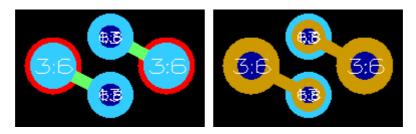

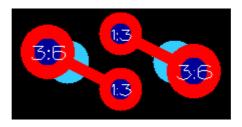

The method used for fanout of BGAs can significantly contribute to the success or failure of the design. Below are some of the considerations:

- Via location relative to BGA pad

- Adjacent (dog-bone)

- o Partial via-in-pad

- o Offset via-in-pad

- o Via-in-pad

- When using a combination of micro-vias and buried-vias, each via span can have its own pattern within the BGA and as such can affect the route-ability of the device.

- Via-in-pad methods provide a good opportunity to increase route density.

- Shifting and aligning the vias is best way to improve routeability.

- Using a complimentary patterns for the micro-vias and buried-vias can improve route-ability

- Goal should be to reduce the overall "effective" number of pins by the time you get to the laminated core, thus reducing the number of layers required to breakout and route the BGA.

# **Theoretical Breakout Methods**

Numerous papers have been written about BGA breakouts, and nearly all of them take a theoretical approach. By "theoretical" I mean the BGA is analyzed outside the context of a real design, often with unrealistic assumptions about power and ground pin assignments, and with little or no regard for signal integrity requirements.

This kind of solution is more of a mathematical exercise in layer reduction as opposed to one that takes careful consideration of balancing the numerous real-world constraints. Unfortunately, reality requires much more than just a mathematical solution. BGAs with over 1500 pins are significantly affected by these additional factors that prevent theoretical solutions from being effective.

This section discusses BGA pin assignments, escape routing, as well as signal and power integrity because these factors affect the decisions about fanout patterns. Deriving fanout patterns in a theoretical realm can actually be fairly simple. Finding effective fanout patterns when all the design and packaging challenges must be considered is a much more difficult problem.

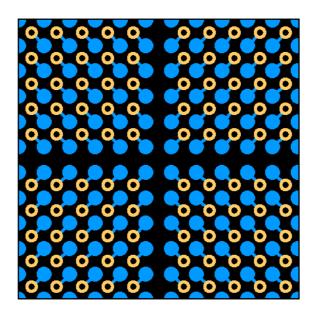

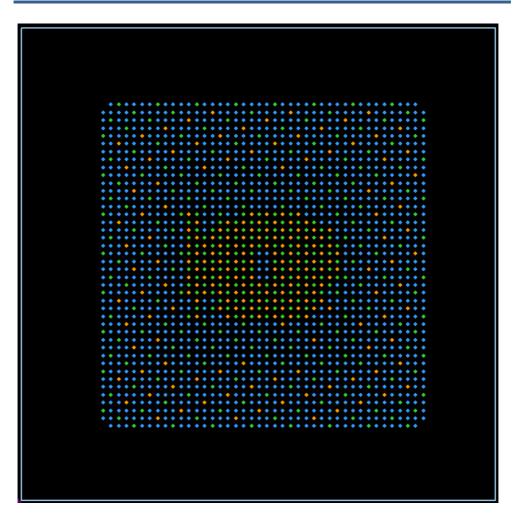

### Distribution of Power and Ground Pins

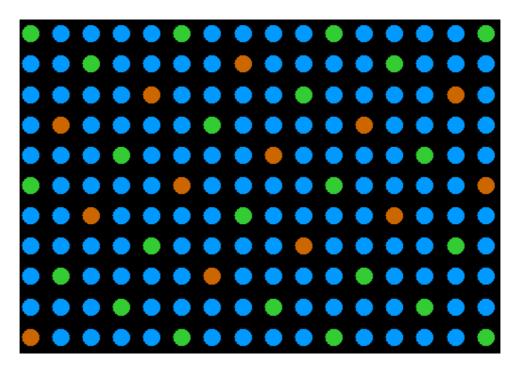

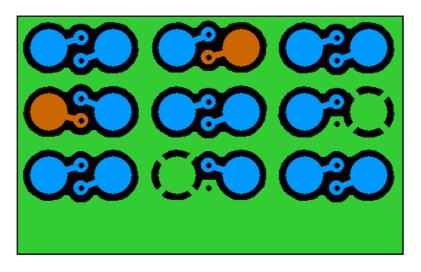

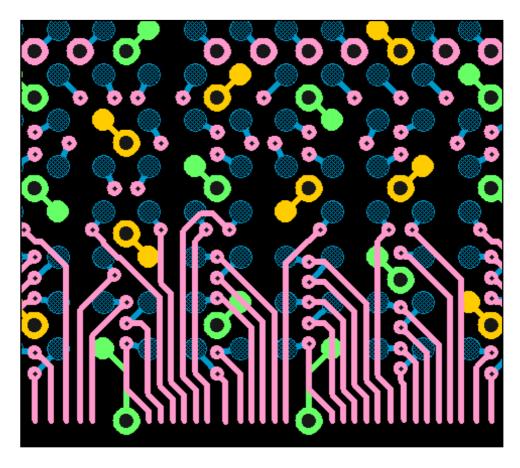

Ideally, it would be nice to have power and ground pins only in the center of the BGA; however, power integrity requires they also be distributed among the signal pins. This distribution is rarely in organized columns and rows, which under some circumstances (HDI, blind and buried vias and a stackup with power and ground on the outer layers) can open up considerable routing space.

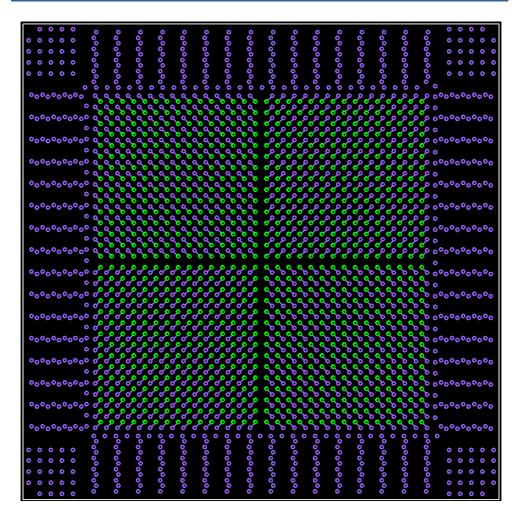

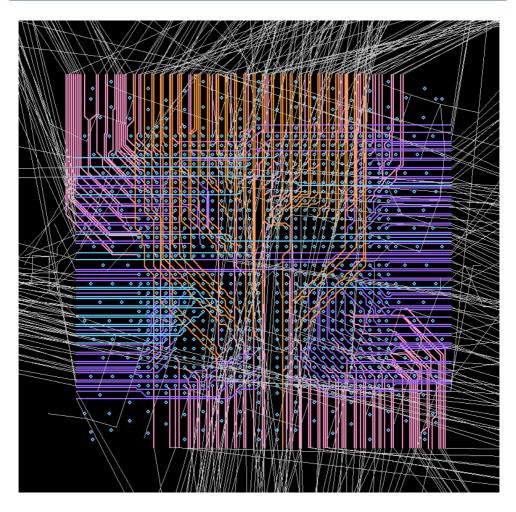

Figure 4-1 shows an ideal distribution of ground pins (green). If the BGA could have the ground pins aligned in this way, and if the mount layer was a ground plane, room is made available on the inner routing layers.

Figure 4-1: Alignment of ground pins

Yet, rarely are the power and ground pins aligned in such a way. In fact, most FPGA vendors sprinkle the power and ground pins or use some

pattern other than columns and rows. The purpose of distributing power and ground pins is to improve the power integrity. Xilinx often uses a "Sparse Chevron" pattern as shown in Figure 4-2. In this figure the ground pins are green and the power pins are brown.

Figure 4-2: Xilinx Sparse Chevron pattern for power and ground pins

There may be some ASICs that have power and ground pins aligned in columns and rows, which indeed could help open up routing channels on inner layers and reduce layer count. However, such an ideal condition is not common and therefore effective fanout and routing solutions must find other ways to reduce the layer count.

### Serial and Parallel Nets

Most large BGAs have a combination of serial and parallel nets which need to be routed as differential pairs and single-ended nets, respectively. Some FPGAs also allow for nets to be programmed as either serial or parallel.

These devices support multiple I/O standards ranging in performance that could require differential routing.

Differential pairs require different trace widths and spacing than singleended nets to maintain the desired impedance and although it is possible to use the same spacing rules inside the BGA area, the impedance discontinuity may become significant in some high-speed circuits.

For example, it is common to have a target of  $50\Omega$  for single-ended nets and  $100\Omega$  for differential pairs. Of course the stackup thicknesses and materials will affect the impedance; yet it is common to see a 0.15mm (6th) for differential pair spacing while single-ended nets can have 0.1mm (4th). Actual trace widths and clearances will vary depending on the specific highspeed and fabrication requirements for each design.

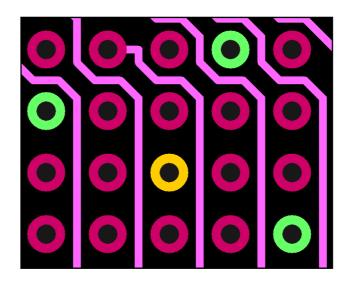

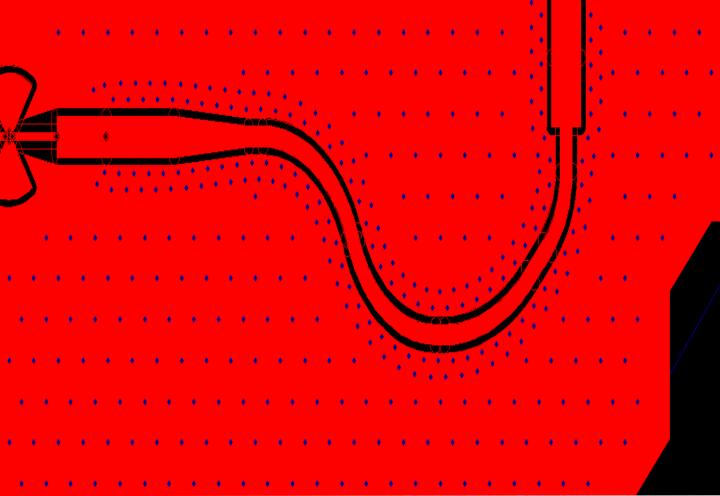

If the fanouts are positioned such that differential pairs need to be split to maintain the trace width and clearance rules, that could also be a significant signal integrity problem. This is illustrated in Figure 4-3.

Figure 4-3: Splitting of differential pairs in BGA fanout via array

The point is that a theoretical fanout and breakout solution that does not take into consideration the potential for varied trace widths and clearances is not very useful. The problem becomes even more difficult when each I/O pin or bank of I/O pins may be programmed to require either differential pair or single-ended routing. An effective fanout solution that enables the most efficient escape routing needs to be flexible enough to support the trace width and clearance requirements for a potential mixture of serial and parallel.

# **Signal Integrity Concerns**

### Via Crosstalk Effects

BGA fanout vias have the potential for allowing significant crosstalk if the spacing between them is inadequate.

### Conditions in which the crosstalk effects should be insignificant:

**Differential pairs**

- Fanout vias, when paired differentially, actually crosstalk very little with each other. That's because the differential signaling localizes the EM fields heavily within each via pair.

- Removing unused pads on through-vias and buried-vias is also recommended because they are a source of noise.

Micro-vias

• When using micro-vias with a span of 2 or 3 layers, the crosstalk potential between vias is much lower than in the case of through-vias or buried-vias.

### Conditions that may enable significant crosstalk:

Fast single-ended nets

- When using through-vias or buried-vias for these nets, vias in close proximity will cause crosstalk.

- This can be mitigated by removing unused pads and back-drilling.

• Routing fast single-ended nets on buildup layers using micro-vias will also greatly reduce crosstalk.

### **Grounded Stitch Vias**

A number of designers have recommended using grounded "stitch vias" near each fanout to provide a clean return path and to reduce crosstalk. Although this method indeed improves signal integrity, it is not a practical solution in the context of large BGAs. The addition of the stitch vias will take up far too much room and also add to the cost of the board fabrication due to the additional routing layers needed to route the device. If there are just a few nets of concern, stitch vias may be a solution. Adding stitch vias around 900 I/Os is not an effective solution. There are other, less expensive methods that can be applied to minimize crosstalk.

When deriving an effective fanout pattern, potential crosstalk between the vias must be considered and managed. Simply spacing them far apart may well eliminate the crosstalk. However, the impact on layer count may be a larger negative. Crosstalk is one of many design problems that needs to be appropriately managed. Maintaining via crosstalk noise below acceptable thresholds as opposed to trying to completely eliminate the effects can enable other goals (such as lowering cost and increasing reliability) to be attained.

# **Minimizing the Variables**

Since there are so many variables such as the stackup, via models and design rules, along with power and signal integrity requirements; it is quite easy to become overwhelmed with the number of possible fanout patterns and not understand their impact on the overall design. There are some principles, however, that can help you choose the appropriate fanout patterns for your particular design.

### **BGA Pin Count**

#### < 800

If the number of pins is fewer than 800, the routing of the BGA does not impact the layer count and the routing challenges will be found elsewhere in the design.

#### 800-1500

Within the range of 800-1500 pins there is a potential that routing of the BGA (especially if there are multiple instances on the board) could present a challenge and therefore the fanout patterns should be carefully determined.

#### >1500

When one or more BGAs in a design have greater than 1500 pins, the routing of these BGAs becomes the most significant contributor to the number of layers in the design and consequently the cost of the board is impacted. An effective set of fanout patterns will likely enable reduction of layer count and board cost.

This document presents fanout patterns for multiple BGAs with >1500 pins that may be effective for your particular design.

#### Design Rules

The design rules used for the fanout patterns will be as listed in these tables:

|                |                        |           |       | Lead Free |

|----------------|------------------------|-----------|-------|-----------|

|                |                        | mm        | mils  | (mm)      |

| 1 mm Pitch BGA | Micro-Via Pad / Hole   | 0.25/0.10 | 10/4  |           |

|                | Blind-Via Pad / Hole   | 0.45/0.20 | 18/8  |           |

|                | Buried-Via Pad / Hole  | 0.45/0.20 | 18/8  |           |

|                | Through-Via Pad / Hole | 0.50/0.25 | 20/10 |           |

|                | Ball Pad               | 0.62      | 25    | .3040     |

|                | Trace Width            | 0.10      | 4     |           |

|                | Diff Pair Clearance    | 0.15      | 6     |           |

|                | Trace-Trace Clearance  | 0.10      | 4     |           |

|                | Via-Trace Clearance    | 0.10      | 4     |           |

|                | Via-Pad Clearance      | 0.10      | 4     |           |

#### Table 4-1: Design rules for 1mm pin pitch

|                  |                       | mm   | mils | Lead Free<br>(mm) |

|------------------|-----------------------|------|------|-------------------|

| 0.8 mm Pitch BGA | Micro-Via Pad         | 0.20 | 8    | ()                |

|                  | Blind-Via Pad         | 0.30 | 12   |                   |

|                  | Buried-Via Pad        | 0.40 | 16   |                   |

|                  | Through-Via Pad       | 0.45 | 18   |                   |

|                  | Ball Pad              | 0.50 | 20   | .3040             |

|                  | Trace Width           | 0.08 | 3    |                   |

|                  | Diff Pair Clearance   | 0.12 | 5    |                   |

|                  | Trace-Trace Clearance | 0.08 | 3    |                   |